# MULTICORE PROGRAMMING PRACTICES Working Group Chairs: David Stewart & Max Domeika President: Markus Levy

#### **Table of Contents**

#### Foreward: Motivation for this Multicore Programming Practices Guide

| Chapter | 1: | Introduction | & | <b>Business</b> | <b>Overview</b> |

|---------|----|--------------|---|-----------------|-----------------|

|---------|----|--------------|---|-----------------|-----------------|

| Chapter 1. Introduction & Business Overview           |    |

|-------------------------------------------------------|----|

| 1.1 Introduction                                      |    |

| 1.2 Goal of MPP                                       |    |

| 1.3 Detailed Description                              |    |

| 1.4 Business Impact                                   |    |

| 1.5 Target Audience                                   |    |

| 1.6 Applying MPP                                      |    |

| 1.7 Areas Outside the Scope of MPP                    |    |

| Chapter 2: Overview of Available Technology           |    |

| 2.1 Introduction                                      | 17 |

| 2.2 Programming Languages                             |    |

| 2.3 Implementing Parallelism: Programming Models/APIs |    |

| 2.4 Multicore Architectures                           |    |

| 2.5 Programming Tools                                 | 18 |

| Charter 2. Analysis and High Land Daries              |    |

| Chapter 3: Analysis and High Level Design             |    |

| 3.1 Introduction                                      |    |

| 3.2 Analysis                                          |    |

| 3.3 Improving Serial Performance                      |    |

| 3.3.1 Prepare                                         |    |

| 3.3.2 Measure                                         |    |

| 3.3.3 Tune                                            |    |

| 3.3.4 Assess                                          |    |

| 3.4 Understand the Application                        | 25 |

| 3.4.1 Setting Speed-up Expectations                   | 25 |

| 3.4.2 Task or Data Parallel Decomposition             |    |

| 3.4.3 Dependencies, Ordering, and Granularity         | 2  |

| 3.5 High-Level Design                                 | 29 |

| 3.5.1 Task Parallel Decomposition                     | 29 |

| 3.5.2 Data Parallel Decomposition                     |    |

| 3.5.3 Pipelined Decomposition                         | 30 |

| 3.5.4 SIMD Processing                                 |    |

| 3.5.5 Data Dependencies                               | 31 |

| 3.6 Communication and Synchronization                 | 33 |

| 3.6.1 Shared Memory                                   | 33 |

| 3.6.2 Distributed Memory                              |    |

| 3.7 Load Balancing                                    |    |

| 5                                                     |    |

| 3.8 Decomposition Approaches                           | 36 |

|--------------------------------------------------------|----|

| 3.8.1 Top-Down or Bottoms-Up                           | 36 |

| 3.8.2 Hybrid Decomposition                             |    |

| Chapter 4: Implementation and Low-Level Design         |    |

| 4.1 Introduction                                       | 40 |

| 4.2 Thread Based Implementations                       |    |

| 4.3. Kernel Scheduling                                 |    |

| 4.4 About Pthreads.                                    |    |

| 4.5 Using Pthreads                                     |    |

| 4.6 Dealing with Thread Safety                         |    |

| 4.7 Implementing Synchronizations and Mutual Exclusion |    |

| 4.8 Mutex, Locks, Nested Locks                         | 45 |

| 4.9 Using a Mutex                                      |    |

| 4.10 Condition Variables                               |    |

| 4.11 Levels of Granularity                             |    |

| 4.12 Implementing Task Parallelism                     |    |

| 4.13 Creation and Join                                 |    |

| 4.14 Parallel Pipeline Computation                     |    |

| 4.15 Master/Worker Scheme                              |    |

| 4.16 Divide and Conquer Scheme                         |    |

| 4.17 Task Scheduling Considerations                    |    |

| 4.19 Affinity Scheduling                               |    |

| 4.20 Event Based Parallel Programs                     |    |

| 4.21 Implementing Loop Parallelism                     |    |

| 4.22 Aligning Computation and Locality                 |    |

| ·                                                      |    |

| 4.22.1 NUMA Considerations                             |    |

| 4.22.2 First-Touch Placement                           |    |

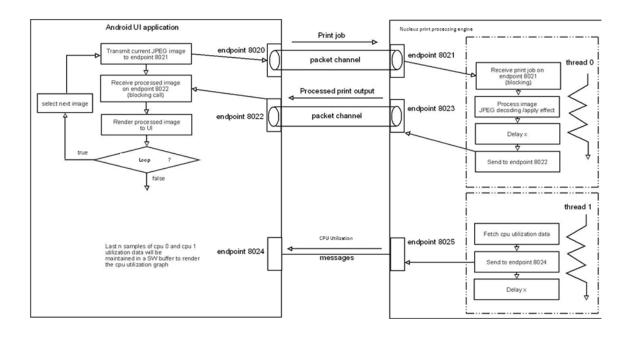

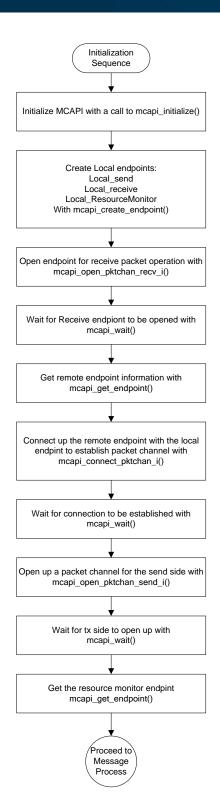

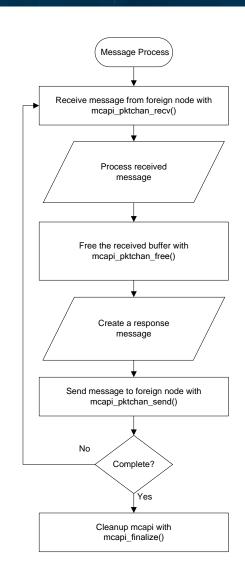

| 4.23 Message Passing Implementations                   | 57 |

| 4.23.1 MCAPI                                           | 57 |

| 4.23.2 MRAPI                                           | 58 |

| 4.23.3 MCAPI and MRAPI in Multicore Systems            | 58 |

| 4.23.5 Using a Hybrid Approach                         | 59 |

| 4.24 Task-based Implementations                        | 60 |

| 4.24.1 MTAPI                                           | 60 |

| 4.24.2 EMB <sup>2</sup>                                |    |

|                                                        | 02 |

| Chapter 5: Debug                                       |    |

| 5.1 Introduction                                       |    |

| 5.2 Parallel Processing Bugs                           |    |

| 5.3 Debug Tool Support                                 |    |

| 5.4 Static Code Analysis                               |    |

| 5.5 Dynamic Code Analysis                              |    |

| 5.6 Active Testing                                                        | 72 |

|---------------------------------------------------------------------------|----|

| 5.7 Software Debug Process                                                | 72 |

| 5.7.1 Debug a Serial Version of the Application                           | 72 |

| 5.7.2 Use Defensive Coding Practices                                      | 73 |

| 5.7.3 Debug Parallel Version While Executing Serially                     | 73 |

| 5.7.4 Debug Parallel Version Using an Increasing Number of Parallel Tasks | 73 |

| 5.8 Code Writing and Debugging Techniques                                 | 73 |

| 5.8.1 Serial Consistency                                                  | 74 |

| 5.8.2 Logging (Code Instrumentation for Meta Data Send and Receive)       |    |

| 5.8.3 Synchronization Points                                              | 75 |

| 5.8.4 Dynamic Analysis Techniques Summary                                 | 76 |

| 5.8.5 Simulation Techniques Summary                                       |    |

| 5.8.6 Stress Testing                                                      | 76 |

| Chapter 6: Performance                                                    |    |

| 6.1 Performance                                                           | 78 |

| 6.2 Amdahl's Law, Speedup, Efficiency, Scalability                        |    |

| 6.3 Using Compiler Flags                                                  |    |

| 6.4 Serial Optimizations                                                  |    |

| 6.4.1 Restrict Pointers                                                   | 80 |

| 6.4.2 Loop Transformations                                                |    |

| 6.4.3 SIMD Instructions, Vectorization                                    |    |

| 6.5 Adapting Parallel Computation Granularity                             | 82 |

| 6.6 Improving Load Balancing                                              |    |

| 6.7 Removing Synchronization Barriers                                     |    |

| 6.8 Avoiding Locks/Semaphores                                             |    |

| 6.9 Avoiding Atomic Sections                                              | 86 |

| 6.10 Optimizing Reductions                                                |    |

| 6.11 Improving Data Locality                                              | 87 |

| 6.11.1 Cache Coherent Multiprocessor Systems                              | 87 |

| 6.11.2 Improving Data Distribution and Alignment                          |    |

| 6.11.3 Avoiding False Sharing                                             |    |

| 6.11.4 Cache Blocking (or Data Tiling) Technique                          |    |

| 6.11.5 Software Cache Emulation on Scratch-Pad Memories (SPM)             |    |

| 6.11.6 Scratch-Pad Memory (SPM) Mapping Techniques at Compile Time        |    |

| 6.12 Enhancing Thread Interactions                                        | 93 |

| 6.13 Reducing Communication Overhead                                      |    |

| 6.14 Overlapping Communication and Computation                            |    |

| 6.15 Collective Operations                                                |    |

| 6.17 Multicore Performance Analysis                                       |    |

| ·                                                                         |    |

| MultiMark<br>ParallelMark                                                 |    |

| 1 alanvivial N                                                            |    |

| MixMark                                                                          | 100 |

|----------------------------------------------------------------------------------|-----|

| Additional Throughput Results With Scaling                                       | 102 |

| Chapter 7: Fundamental Definitions                                               |     |

| 7.1 Fundamental Definitions Introduction                                         | 105 |

| 7.2 Fundamental Multicore Definitions (Hardware)                                 |     |

| 7.3 Fundamental Multicore Definitions (Configuration)                            |     |

| 7.4 Fundamental Multicore Definitions (Software)                                 | 107 |

| Appendix A: MPP Architecture Options                                             |     |

| A.1 Homogeneous Multicore Processor with Shared Memory                           | 108 |

| A.2 Heterogeneous multicore processor with a mix of shared and non-shared memory |     |

| A.3 Homogeneous Multicore Processor with Non-shared Memory                       |     |

| A.4 Heterogeneous Multicore Processor with Non-shared Memory                     |     |

| A.5 Heterogeneous Multicore Processor with Shared Memory                         | 109 |

| Appendix B: Programming API Options                                              |     |

| B.1 Shared Memory, Threads-based Programming                                     | 110 |

| B.1.1 Pthreads (POSIX Threads)                                                   |     |

| B.1.2 GNU Pth (GNU Portable Threads)                                             |     |

| B.1.3 OpenMP (Open Multiprocessing)                                              | 111 |

| B.1.4 Threading Building Blocks (TBB)                                            | 111 |

| B.1.5 Protothreads (PT)                                                          |     |

| B.1.5 Embedded Multicore Building Blocks (EMB²)                                  |     |

| B.2 Distributed Memory, Message-Passing Programming                              | 112 |

| B.2.1 Multicore Communications API (MCAPI)                                       | 112 |

| B.2.2 Message Passing Interface (MPI)                                            | 112 |

| B.2.3 Web 2.0                                                                    | 112 |

| B.3 Platform-specific Programming                                                | 113 |

| B.3.1 Open Computing Language (OpenCL)                                           | 113 |

| Appendix C: Parallel Programming Development Lifecycle                           |     |

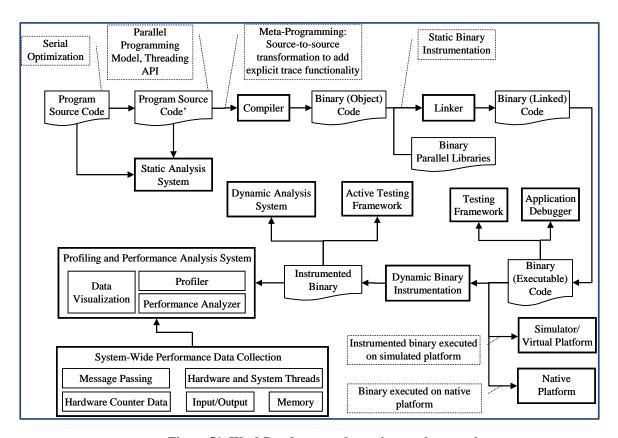

| C. 1 Introduction to Parallel Tool Categories                                    | 114 |

| C.1.1 Compilers                                                                  | 115 |

| C.1.2 Static Code Analyzers                                                      |     |

| C.1.3 Debuggers                                                                  | 116 |

| C.1.4 Dynamic Binary Instrumentation                                             |     |

| C.1.5 Dynamic Program Analysis                                                   |     |

| C.1.6 Active Testing                                                             |     |

| C.1.7 Profiling and Performance Analysis                                         |     |

| C.1.8 System-wide Performance Data Collection                                    | 11/ |

#### Appendix D

| References |

|------------|

|------------|

| Figure 1. Serial performance tuning approach. Four key steps: prepare, measure, tune, assess    | 21    |

|-------------------------------------------------------------------------------------------------|-------|

| Figure 2. Task parallel decomposition example.                                                  | 26    |

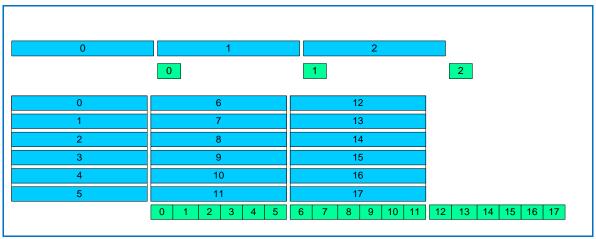

| Figure 3. Data parallel decomposition example.                                                  | 27    |

| Figure 4.Task parallel image processing example.                                                | 29    |

| Figure 5. Data parallel image processing example.                                               | 30    |

| Figure 6. Pipelined edge detection                                                              | 31    |

| Figure 7. Three types of data dependency examples                                               | 32    |

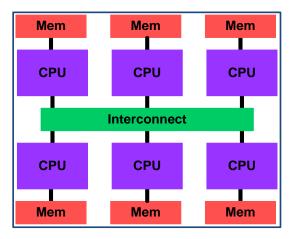

| Figure 8. Processing units share the same data memory.                                          | 33    |

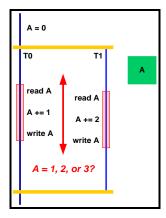

| Figure 9. Shared data synchronization.                                                          | 34    |

| Figure 10. Distributed memory architecture.                                                     | 35    |

| Figure 11. Example depicts 2-stage pipeline combining data and pipeline decomposition           | 37    |

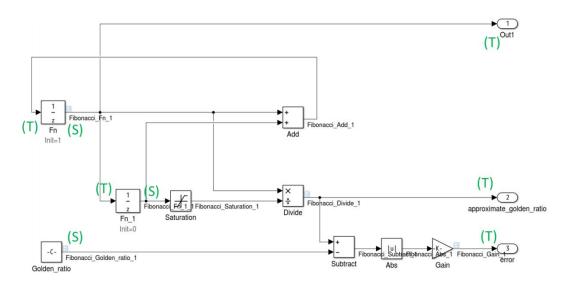

| Figure 12. Model for Fibonacci function                                                         | 38    |

| Figure 13. Model partitioning.                                                                  | 38    |

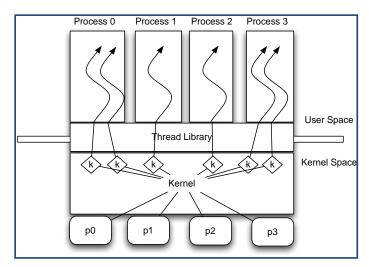

| Figure 14. Hybrid threading model.                                                              | 40    |

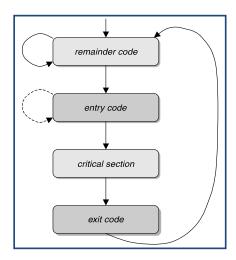

| Figure 15. Critical section protection requirements.                                            | 43    |

| Figure 16. A common C++ scope-locking technique.                                                | 44    |

| Figure 17. A partial example of initializing and locking a critical section with a mutex        | 46    |

| Figure 18. Simple concurrent queue using two condition variables and a mutex.                   | 47    |

| Figure 19. Pthreads creation and join.                                                          | 50    |

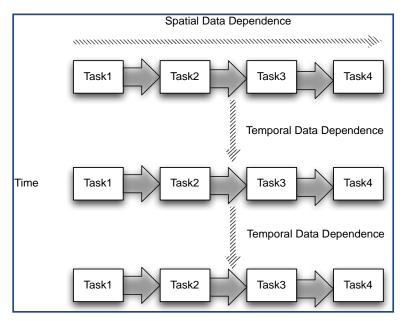

| Figure 20. Parallel pipeline system with temporal and data dependencies                         | 51    |

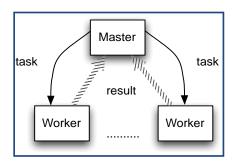

| Figure 21. Master/worker scheme supports dynamic task distribution.                             | 51    |

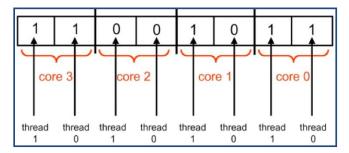

| Figure 22. Code snippet using bitmap mask for cache affinity scheduling.                        | 53    |

| Figure 23. Affinity mask                                                                        | 54    |

| Figure 24. An example of loop parallelism using Pthreads.                                       | 55    |

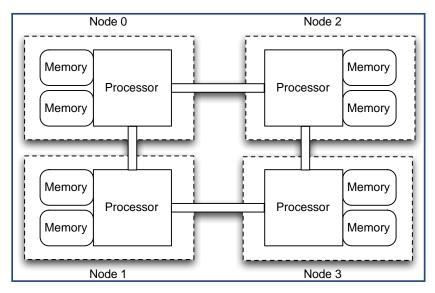

| Figure 25. With NUMA architecture, each processor core connects to a node with dedicated memory | y. 56 |

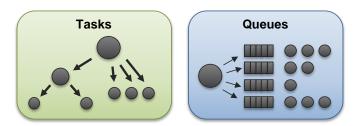

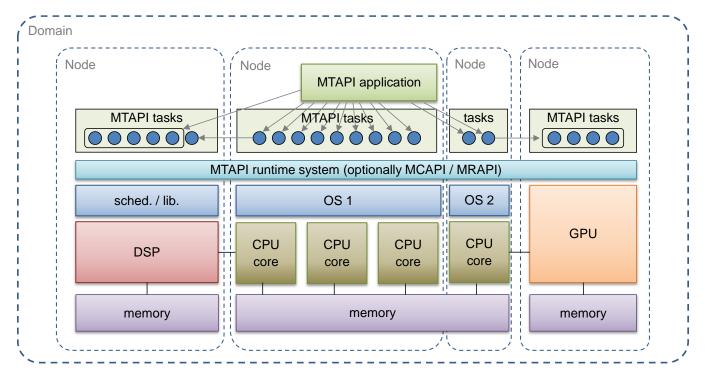

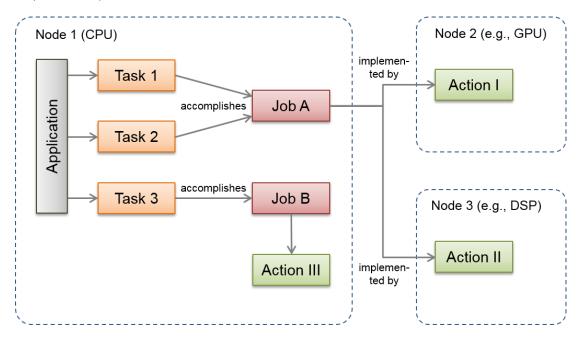

| Figure 26. Basic MTAPI programming models                                                       | 60    |

| Figure 27. Example for MTAPI-based architecture                                                 | 61    |

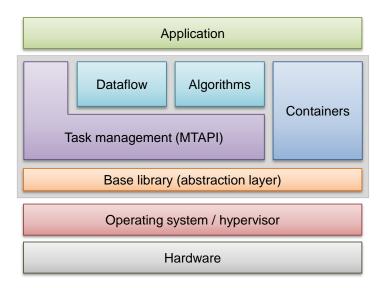

| Figure 29. EMB <sup>2</sup> components                                                          | 63    |

| Figure 30. Example for task creation and synchronization                                        | 63    |

| Figure 31. Example for parallel loop                                                            | 64    |

| Figure 32. Code sample show in data race condition.                                             | 67    |

| Figure 33. Code sample showing a Livelock condition                                             | 68    |

| Figure 34. Serial consistency example                                                           | 74    |

| Figure 35. Logging example.                                                                     | 75    |

| Figure 36. Code sample restricting pointers.                                                    |       |

| Figure 37. Sample code showing the unroll-and-jam loop transformation.                          | 81    |

| Figure 38. Example code using the SSE intrinsic library.                                        | 82    |

| Figure 39. Divide and Conquer approach.                                                         | 83    |

| Figure 41. Parallel reductions.                                                                 | 86    |

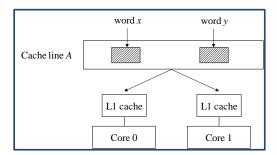

| Figure 41. False sharing situation.                                                             | 89    |

| Figure 42. Cache-line padding example.                                          | 89  |

|---------------------------------------------------------------------------------|-----|

| Figure 43. Cache blocking example                                               | 91  |

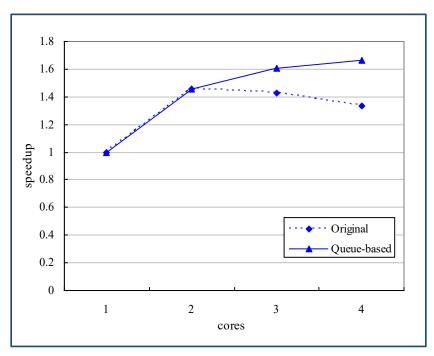

| Figure 44. Performance comparison utilizing queue-based memory access           | 94  |

| Figure 45. Example code broadcasting data with MPI.                             | 96  |

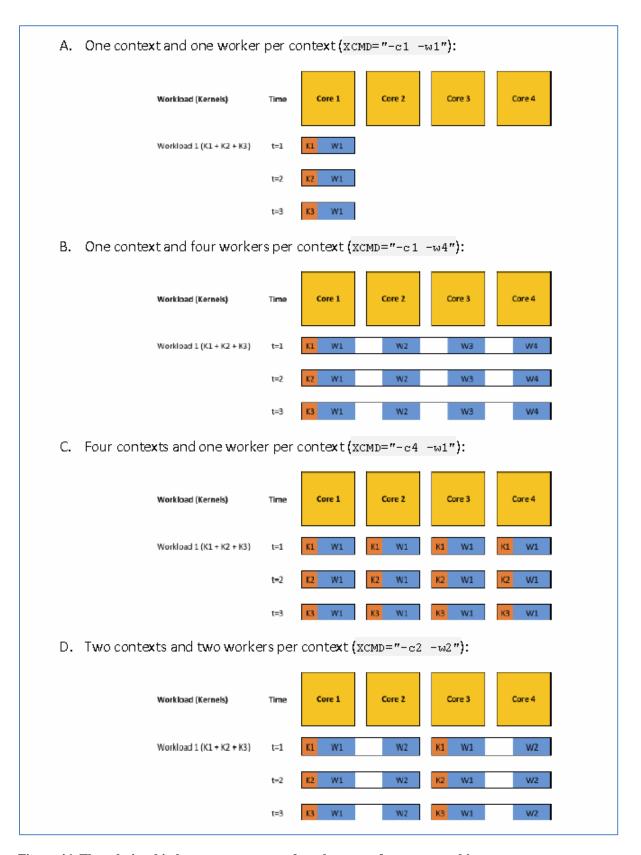

| Figure 46. The relationship between contexts and workers on a four-core machine | 99  |

| Figure 47. Sample scores on a simulated 16-core platform                        | 101 |

| Figure 48. Sample scores from two dual-core platforms running at 2 GHz          | 101 |

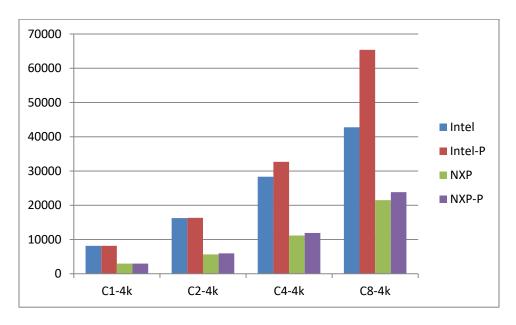

| Figure 49. Scaling with 4kbyte data sizes                                       | 103 |

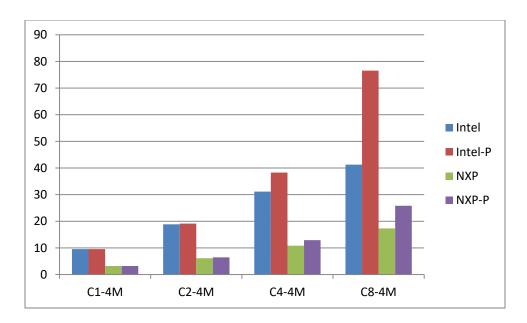

| Figure 50. Scaling with 4Mbyte data sizes.                                      | 103 |

| Figure 51. Workflow between the various tool categories.                        | 115 |

# FOREWARD: MOTIVATION FOR THIS MULTICORE PROGRAMMING PRACTICES GUIDE

#### Markus Levy, Multicore Association President

The Multicore Association was founded in May 2005, back in the pioneering days of multicore technology. To this day, the primary goal of the MCA is to develop an extensive set of application programming interfaces (APIs) and the establishment of an industry-supported set of multicore programming practices and services.

When the Multicore Programming Practices working group (MPP) formed 4+ years ago, it was (and still is) a known fact that C/C++ was going to be the predominant programming language for at least the better part of the next decade. While the industry was waiting for long-term research results to change the programming infrastructure, the multicore programmability gap was continuously expanding, pointing out an obvious need for a group of like-minded methodology experts to create a standard "best practices" guide.

Through the guidance of Max Domeika (Intel) and David Stewart (CriticalBlue), the Multicore Association created this one-of-a-kind document, providing best practices for writing multicore-ready software using C/C++ without extensions, describing a framework of common pitfalls when transitioning from serial to parallel code, and offering insight to minimizing debugging efforts by reducing bugs.

Of course, the only problem with creating this kind of guide is that it's really a work in progress. As a matter of fact, even at the onset of this monumental project, we realized that the biggest challenge was deciding what <u>not</u> to include (at least in the first version). So therefore, on one hand I personally wish to thank the working group members, and on the other hand, I'm inviting you to step forward and join the Multicore Association effort to help evolve this MPP Guide.

Primary contributors to the Multicore Programming Practices Guide include:

Hyunki Baik (Samsung)

François Bodin (CAPS entreprise)

Ross Dickson (Virtutech/Wind River)

Max Domeika (Intel)

Masato Edahiro (Nagoya University)

Scott A. Hissam (Carnegie Mellon University)

Skip Hovsmith CriticalBlue)

James Ivers (Carnegie Mellon University)

Markus Levy (EEMBC and The Multicore Association)

Ian Lintault (nCore Design)

Stephen Olsen (Mentor Graphics)

Tobias Schuele (Siemens Corporate Technology)

David Stewart (CriticalBlue)

Peter Torelli (EEMBC)

## CHAPTER 1: INTRODUCTION & BUSINESS OVERVIEW

#### 1.1 Introduction

Multicore processors have been available for many years; however, their widespread use in commercial products and across multiple market segments has only recently occurred. This 'multicore era' transpired because processor architects ran into power & performance limits of single core processors. The multicore era shifts more of the responsibility for performance gains onto the software developer who must direct how work is distributed amongst the cores. In the future, the number of cores integrated onto one processor is expected to increase, which will place even greater burden on the software developer. Like many new eras in the computer industry, numerous supporting software development tools and technologies have been introduced with the aim of helping developers obtain maximum performance benefit with minimal effort. One of the potential challenges that may hinder developers is the conflict between an intrinsic quality of developing for multicore processors and the inertia of existing software.

Prior to the multicore processor era, developers obtained performance increases through processor upgrades and the inherent clock frequency boosts and microarchitecture improvements. These upgrades required minimal software changes. Obtaining performance increases in the multicore era requires developers to invest in significant software modifications to, in effect, transform current sequential applications into parallel ones. This modification is nontrivial and introduces new challenges, spanning the traditional development phases of program analysis, design, implementation, debug, and performance tuning.

In stark contrast, the inertia of existing software is undeniable. To meet tight deadlines, development projects rarely have the freedom to make wholesale changes to applications, and instead limit risk by minimizing them. This means that a developer considering a move to multicore processors may not have the luxury of taking on a new parallel programming language or even re-architecting the application to support widespread concurrency. Instead, many development projects in the computing industry are adopting an evolutionary approach to enabling multicore processors. This approach employs existing programming tools and technology and a systematic method of introducing and debugging concurrency in existing software.

The Multicore Association (MCA) Multicore Programming Practices (MPP) guide is a detailed set of best practices for employing this evolutionary approach to multicore development. The following sections detail the goal of the MPP guide, the target audience, how to apply the MPP guide, and areas not covered.

#### 1.2 Goal of MPP

The Multicore Programming Practices guide details a concise set of best practices in software development for multicore processors using existing technology and existing software. In writing this document, the MPP working group made decisions and compromises in *what and how much* this document targets.

The following are thoughts on some of the higher level decisions made:

- API choices Pthreads and MCAPI were selected for several reasons. These two APIs cover

the two main categories of multicore programming shared memory parallel programming and

message passing. Second, Pthreads is a very commonly used API for shared memory parallel

programming. MCAPI is a recently introduced API, but is novel in being a message passingbased multicore API that specifically targets embedded homogeneous and heterogenuous

applications.

- Architecture categories The architecture categories (homogeneous multicore with shared memory, heterogeneous multicore with mix of shared and non-shared memory, and homogeneous multicore with non-shared memory) are in priority order and reflect the group's assessment of use in embedded applications. Admittedly, the second category is a superset of the first and third. The motivation for listing these three categories separately is due to the widespread and common use of techniques associated with the first and third, namely shared memory parallel techniques and process-level parallelism. The following paragraphs dissect this goal and offer more detail.

#### 1.3 Detailed Description

A concise set of best practices is a collection of best known methods for accomplishing the task of development for multicore processors. The intent is to share development techniques that are known to work effectively for multicore processors thus resulting in reduced development costs through a shorter time-to-market and a more efficient development cycle for those employing these techniques.

The phases of software development discussed in MPP and a summary of each follows:

- Program analysis and high level design is a study of an application to determine where to add concurrency and a strategy for modifying the application to support concurrency.

- Implementation and low level design is the selection of design patterns, algorithms, and data structures and subsequent software coding of the concurrency.

- Debug comprises implementation of the concurrency in a manner that minimizes latent concurrency issues, enabling of an application to be easily scrutinized for concurrency issues, and techniques for finding concurrency issues.

- Performance concerns improving turnaround time or throughput of the application by finding and addressing the effects of bottlenecks involving communication, synchronization, locks, load balancing, and data locality.

- Existing technology includes the programming models and multicore architectures detailed in the guide and are limited to a few that are in wide use today.

- Existing software, also known as legacy software, is the currently used application as represented by its software code. Customers using existing software have chosen to evolve the implementation for new product development instead of re-implementing the entire application to enable multicore processors.

#### 1.4 Business Impact

Readers of the MPP guide, who apply the detailed steps, may save significant costs in development projects. Cost savings can be applied to developer efficiency in analyzing and designing the implementation, a reduced number of bugs in the implementation, and increased likelihood of the implementation meeting performance requirements. These savings lead to faster time-to-market and lower development cost.

#### 1.5 Target Audience

The MPP guide is written specifically for engineers and engineering managers of companies considering or implementing a development project involving multicore processors and favoring the use of existing multicore technology.

Specifically, the benefits of this guide to the specific target audience are summarized below:

- Software developers who are experienced in sequential programming will benefit from reading

this guide as it will explain new concepts which are essential when developing software

targeted at multicore processors.

- Engineering managers running technical teams of hardware and software engineers will benefit from reading this guide by becoming knowledgeable about development for multicore processors and the learning curve faced by their software developers.

- Project managers scheduling and delivering complex projects will benefit from reading this

guide as it will enable them to appreciate, and appropriately schedule, projects targeting

multicore processors.

- Test engineers developing tests to validate functionality and verify performance will benefit from reading this guide as it will enable them to write more appropriate and more efficient tests for multicore-related projects.

#### 1.6 Applying MPP

The MPP guide is organized into chapters based upon software development phases. Following a brief introduction, each chapter includes either a process description or topic-by-topic coverage containing the technical details or both. The MPP guide provides more than a cursory review of a topic and strives to offer a succinct, but detailed enough description targeting the average developer.

#### 1.7 Areas Outside the Scope of MPP

The MPP guide does not address every possible mechanism for parallel programming - there are simply too many different technologies and methods. The guide constrains coverage to existing and commonly used technology. Many of the techniques detailed in the guide can be generally applied to other programming models, however, this guide does not comment on the specifics necessary in a remapping. Chapter 7 contains comments on many of the technologies and methods, but the discussion is intended to be informational and not specific to the best practices documented in the previous chapters.

In particular, the areas outside the scope of the best practices portion of the MPP guide are:

- Languages other than C and C++ and extensions to C and C++ that are not part of the C and C++ ISO standard or are proprietary extensions to the standards;

- Coding style guidelines; and

- Architectures and programming models other than those specified in Chapter 2. This includes C & C++ compatible parallel libraries other than those specified in Chapter 2.

### CHAPTER 2: OVERVIEW OF AVAILABLE TECHNOLOGY

#### 2.1 Introduction

Multicore programming tools and models include items such as software development tools, programming languages, multicore programming APIs, and hardware architectures. While the programming practices covered in this guide are exemplified on these specific tools and models, our intent is for these practices to be generally applicable. This chapter specifies the programming languages, multicore programming APIs, and hardware architectures assumed in the programming practices documented in the later chapters.

#### 2.2 Programming Languages

The MPP guide employs standard C and C++ as the implementation languages because these are the predominant languages used in embedded software development. The C language as specified in "ISO/IEC 9899:1999, Programming Language C" is used. The C++ language as specified in "ISO/IEC 14882, Standard for the C++ Language" is used. For both languages, we did not use any nonstandard extensions, either commercial or research oriented.

#### 2.3 Implementing Parallelism: Programming Models/APIs

There are several types of parallelism used in multicore programming, namely Task Level Parallelism (TLP), Data Level Parallelism (DLP), and Instruction Level Parallelism (ILP). The MPP guide focuses on TLP and DLP, however all three types of parallelism play a role in design and implementation decisions.

The MPP guide uses two multicore programming APIs, Pthreads<sup>i</sup> and Multicore Communications API (MCAPI<sup>ii</sup>), for its examples. This will allow us to provide coverage of two categories of multicore software development - shared memory programming and message-passing programming. We chose these two APIs because they are commonly used APIs within these two software development paradigms.

#### 2.4 Multicore Architectures

The MPP guide targets three classes of multicore architectures: homogeneous multicore with shared memory, heterogeneous multicore with mix of shared and non-shared memory, and homogeneous multicore with non-shared memory<sup>iii</sup>. These three classes are the predominant architectures employed in embedded projects and they are different enough so that the set of practices that apply to each are substantially disjointed. The underlying communication fabric is outside the scope of this document and in most cases is irrelevant to the software developer.

A homogeneous multicore processor with shared memory is a processor comprised of multiple processor cores (2 to n cores) implementing the same ISA and having access to the same main memory.

A heterogeneous multicore processor with a mix of shared and non-shared memory is a processor comprised of multiple processor cores implementing different ISAs and having access to both main memory shared between processor cores and local to them. In this type of architecture, local memory refers to physical storage that is only accessible from a subset of a system. An example is the memory associated with each SPE in the Cell BE processor from Sony/Toshiba/IBM. It is generally necessary to state what portion of the system the memory is local to, as memory may be local to a processor core, a processor, an SoC, an accelerator, or a board.

A homogeneous multicore processor with non-shared memory is a processor comprised of multiple processor cores implementing the same ISA and having access to local, non-shared main memory.

#### 2.5 Programming Tools

The software tools employed in this guide and details of use are summarized as follows:

- GNU gcc version 4.X compiler used for all C examples

- GNU g++ version 4.X compiler used for all C++ examples

# CHAPTER 3: ANALYSIS AND HIGH LEVEL DESIGN

#### 3.1 Introduction

This chapter discusses program analysis techniques used to uncover opportunities to exploit parallel behavior and the dependencies which constrain that behavior. Analysis results are strongly affected by the use of representative benchmarks and realistic workloads. High level design decisions, including choice of algorithm, selection of platform architecture, and identification of appropriate parallel design patterns, are then made which will optimize the multicore implementation to meet critical application metrics such as performance, power, footprint, and scalability.

#### 3.2 Analysis

To effectively exploit multicore resources, you must parallelize your program. However, several steps should first be taken before introducing parallelism. This section describes two such activities—improving the program's serial performance<sup>iv</sup> and understanding the program.

#### 3.3 Improving Serial Performance

The first step in redesigning your program to exploit multicore resources is to optimize its serial implementation because serial performance tuning is typically easier, less time consuming, and less likely to introduce bugs. Serial improvement will reduce the gap between where you are and your performance goal, which may mean that less parallelization is needed. It also allows parallelization to focus on parallel behavior, rather than a mix of serial and parallel issues.

It is important to remember, though, that serial optimization is *not* the end goal. We want to optimize carefully, applying only changes that will facilitate parallelization and the performance improvements that parallelization can bring. In particular, serial optimizations that interfere with, or limit parallelization should be avoided. For example, avoid introducing unnecessary data dependencies or exploiting details of the single core hardware architecture (such as cache capacity).

Developers are familiar with many techniques that can be used to improve a program's serial performance; in fact, there is a wealth of public material (e.g., articles, books, tools, and accumulated wisdom). But haphazard application of such improvements is generally a bad idea.

"Programmers waste enormous amounts of time thinking about, or worrying about, the speed of noncritical parts of their programs, and these attempts at efficiency actually have a strong negative impact when debugging and maintenance are considered. We should forget about small efficiencies, say about 97% of the time: premature optimization is the root of all evil."

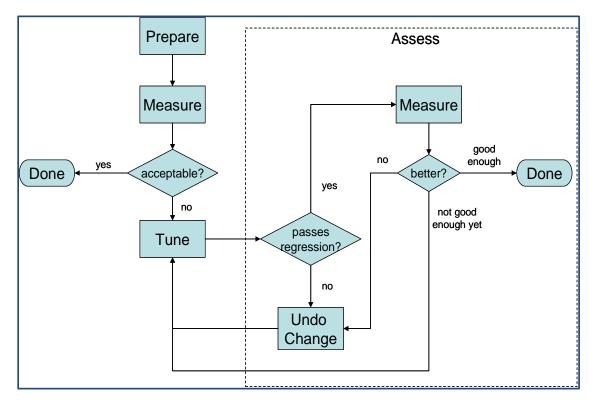

Instead, discipline and an iterative approach are the keys to effective serial performance tuning (Figure 1). Use measurements and careful analysis to guide decision making, change one thing at a time, and meticulously re-measure to confirm that changes have been beneficial.

Figure 1. Serial performance tuning approach. Four key steps: prepare, measure, tune, assess.

The following sections provide short descriptions of the steps in this approach, but each topic is richer than can be reasonably covered in this document. There has been a great deal of useful work in performance analysis and performance tuning and most of it is applicable when preparing for multicore (though the effects of parallelization changes are more sensitive to the order in which the changes are applied).

#### 3.3.1 Prepare

Assemble a collection of regression tests and benchmarks against which to improve the program's performance. Before making any changes, think about your objectives and assemble the resources that will help you achieve them efficiently and reliably.

- What are your goals? Improving a program's performance can be a complicated, time consuming, and error prone task. Stop when you've reached "good enough" results.

- What operational scenarios are most important? Any improvements made will be based on data

from observation of the program's execution, but which scenarios are most important? You

could focus on steady state operations, heavy load conditions, error recovery scenarios, or

some balance of such scenarios.

- What performance metric makes sense for your program? Perhaps it's the time to process a unit of work, or maybe the number of units of work completed in a unit of time. Know what to measure so you can quantify goals or know that you've met them.

Construct a set of benchmarks (uses of the program over specific data and operations) over which you will collect performance data. All optimizations will be relative to the benchmarks, so carefully choose the scenarios for which performance most needs to be improved. Also include cases that vary the workload so that you can see how performance scales (at least three data points are needed to differentiate linear from non-linear scaling). vi

Performance optimizations are often trade-offs with some other concern, such as memory consumption, code maintainability, or portability. Know how much you are willing to compromise in any of these areas.

Serial performance tuning is an iterative process that involves repeated execution of your program, both to measure performance and ensure that correct functionality is preserved, so make sure you have a good regression suite before you start (it should go without saying that the program passes all tests before starting).

#### 3.3.2 Measure

After preparations are complete, the next task is to utilize your benchmarks and understand the baseline performance of your program. Development tools, such as profilers, are typically used to measure performance. A profiler is a tool that observes the execution of a program and collects measures of its performance. Several different approaches are used for profiling:

- Sampling: A sampling profiler takes measurements at regular intervals. vii

- Instrumentation: An instrumention-based profiler typically compiles or links additional instructions into the program for measurement.

- Emulation or simulation: These approaches execute the program in an environment that emulates or simulates (e.g., through interpretation) the execution environment.

The quality of the performance data varies in several ways, two of which are completeness and resemblance of "real performance." Sampling only measures at regular intervals, generating incomplete insight into program behavior. Non-sampling approaches produce complete data, with respect to the measurement granularity. Any profiling approach, however, has some effect on how closely the measurements resemble execution in the absence of measurement. Low overhead approaches more closely resemble typical execution than those with high overhead, such as instrumentation or interpretation, which may alter the timing properties of the program in significant ways.

Output differs from tool to tool in both granularity and format. Profilers typically measure data relative to functions, with simple measures being the time at which each function call and return occurs. Some profilers capture information at a finer granularity or allow the user add instrumentation points (e.g., encompassing interesting loops).

Profiler output varies considerably, from simple reports to sophisticated GUIs with controls for filtering and sorting. Two common forms of output are:

- A flat profile is generally a tabular report of statistics organized by function, such as how much execution time was spent in a function (by percent and units of time) and the number of times the function was called.

- A call graph shows execution time, again by function, relative to call chains. A call graph will show which functions were called by a given function, how many times, and how much execution time was used.

Typically, you want to use both forms of output. A flat profile is a good way to quickly find where large portions of time are being spent (e.g., a single function that consumes 60% of the time). A call graph is a good way to see where a function is being used.

Profiler(s) choice is based on a number of the usual criteria, such as availability/cost, target platform, experience, and so on. Use at least one profiler that measures how much of your execution time is spent outside of your program (e.g., in system calls) to assemble a more complete performance picture. When developing an embedded system, you may need to use an emulation- or simulation-based profiler before target hardware is available or to compensate for lack of a persistent store for measurements in the target device.

#### 3.3.3 Tune

An important rule of thumb in performance tuning is "only change one thing at a time." Each tuning iteration, use the measurements you gathered through profiling to look for the biggest improvement you can reasonably make. Wiii Remember that you will also be making substantial changes when parallelizing your program, so it's usually best to stick with the "low-hanging fruit" or big wins when improving the serial program's performance. Changing an algorithm that consumes a large portion of time to scale linearly rather than logarithmically, for instance, would be a good example of a change worth making (for clarification, this sentence only refers to the scaling, which depends on the number of cores, and not to the algorithm's complexity, which depends on the size of the input data). In general, favor changes that reduce computation over those that minimize data footprint. At this stage, we want to focus on reducing the program to the essential computations needed to function correctly.

Start by looking through your measurements for hotspots. Hotspots are areas in your program that use disproportionate percentages of your execution time, and can be found using flat profiles. Start with hotspots for a simple reason: a performance improvement in frequently executed code will yield better overall improvement than a similar improvement in infrequently executed code. That is, a 10% improvement in a function using 50% of total execution time is an overall improvement of 5%; a 10% improvement in a function using 5% of total execution time is only an overall improvement of 0.5%. Beware of diminishing returns.

Once you select a hotspot for examination, think about why it is consuming so much time and whether that is reasonable.

- Computing: executing the instructions is the first thing we tend to think about.

- Is an appropriate algorithm used; review the profiling data for different workloads to see if it's scaling as you would expect.

- Are all computations needed. You may be able to hoist calculations out of a loop or use lookup tables to reduce computation.

- Are you using the right types and data structures? Moving larger chunks of memory around typically takes longer (e.g., using floats is often faster than using doubles). Consider the impact of different language constructs on your platform (e.g., the overhead that is necessary to support exception handling).

- Is your program decomposition good? Use inlining or refactoring if you have functions whose execution time isn't significantly larger than call/return overhead.

- Think about your persistence strategies. Re-initializing and re-using a data structure (or class) can be more efficient than creating a new one.

- Waiting: some operations just have to spend time waiting, which is particularly problematic in serial programs. I/O operations like network or file system access take a long time, as does user interaction. Examine your caching strategy for some improvements, but using concurrency is the typical solution. Avoid introducing concurrency at this point, but note the dependency. This will factor into your parallelization strategy.

- Working with large data sets can cause programs to frequently move data in and out of memory. Reducing unnecessary memory moves can be a big help. Memory profilers are good tools for understanding and improving your memory use.

- Though it could improve serial performance, avoid reorganizing your data for locality (i.e., keeping data used together close in memory, which could allow a single move instead of several smaller moves). This kind of optimization is better performed as part of parallelization, when factors like cache width and policy are considered.

As you examine each hotspot, use several sources of information. Beyond the code itself, you can also get a lot of quick information from the call graph generated by a profiler. By looking at calls made by or to a function, you gain more insight into how it's used and what it does. In particular, walking back up the call graph (callers of the function) may lead you to a hotspot that is not a leaf node of the call graph.

#### 3.3.4 Assess

Each time you make a change to your program, stop and assess the effect. A "good change" is one that does not introduce bugs and that either directly or indirectly enables additional changes which improve the performance metrics you identified in the *Prepare* step. Assess these criteria by re-running your regression suite and re-measuring the program using your benchmarks.

If the regression fails or your performance is worse than before the change, then you misunderstood something about the program or your change. Study the program again, before and after the change, to understand the cause of the failure. If it cannot be fixed, back out the change and return to the Tune step. Re-examine the hotspot and try to apply different changes before moving on to the next hot spot.

If the regression passed and your performance improved, make sure the change is also acceptable with regards to your other concerns. For example, it might be important to preserve the portability properties that your program started with. Such criteria are often more difficult to validate in an automated way, but should be part of your mental checklist.

#### 3.4 Understand the Application

Regardless of the technique used to transform the application from one that processes sequentially to one that processes concurrently, having a thorough understanding of the problem being solved cannot be avoided. This understanding can come from a variety of sources, including documentation, discussions with the application's developers, and profiling data.

As discussed in the following sections, some aspects of an application's behavior are particularly relevant to parallelization, such as a thorough understanding of computational and data dependencies. A good application analysis will help to determine which dependencies are inherent in solving the problem and which are artificial, perhaps introduced as part of a serial optimization.

#### 3.4.1 Setting Speed-up Expectations

Generally there are two reasons for splitting up and re-architecting an application for parallelization: solving large problems and speed-up. Solving large problems is achieved not only by distributing the work across cores, but (sometimes) also by distributing the work across processors due to the sheer size of the data which makes the problem too large for a single processor<sup>ix</sup>. Speed-up will be the primary driver for the discussion here (based on the assumption that the legacy application being ported to the multicore platform is already properly sized for data and memory requirements).

Speed-up is achieved by effectively load balancing work across the cores to minimize execution time, but there are limits to what is reasonable. For example, some code segments cannot be effectively parallelized. Amdahl's Law (see Section 6.2) expresses the maximum expected benefit for improving a portion of an application. If the serial execution time of a portion accounts for 80% of the total time, and that portion will be spread across eight cores, the result would be at best 3.3 times faster. If that same portion only accounted for 20% of serial execution time, the same parallelization would be at best 1.2 times faster. These are maximum expected improvements - various overhead factors (e.g., for coordination) will further reduce the benefit.

The effort to parallelize the application should be justified by an objective analysis of the application, the effort required to make the change, and the realistic expectations from the effort.

#### 3.4.2 Task or Data Parallel Decomposition

From the application's profile it should be possible to find the more computationally-intensive sections of the application (e.g., hotspots identified from the flat profile generated from measures of the serial application). The computational nature of these sections will likely fall into one of two general forms of parallel decomposition: task or data parallel. (Note: Task parallel is sometimes referred to as function parallel).

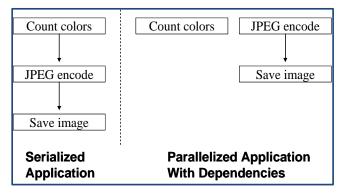

Task parallel decomposition is where the solution to a problem could be envisioned as a sequence of steps which could be accomplished concurrently, which are absolutely or relatively independent of each other, to achieve the same outcome regardless of the order in which those tasks are carried out. Absolutely independent of each other means that the tasks share no data and that no synchronization between the steps must occur (very uncommon). Relatively independent of each other, the more common situation, means that such tasks share data and at certain times the tasks must synchronize their activities. One example of task parallel decomposition is an image processing and capture application in which a bitmap from a camera is received and the application performs three operations:

- Count the number of unique colors in the image

- Convert the bitmap to a JPEG

- Save the image to disk.

In the serialized application, these activities are sequential (Figure 2). In the task parallelized version of this application, two tasks can be done in parallel since there are no dependencies between them, but the third task to save the image can only be done after the bitmap is converted to JPEG—thus requiring synchronization between the task that performs the encoding and the task that saves the image. If the application were only required to save the original bitmap captured from the camera and not the converted JPEG, there would be absolutely no dependencies between the three tasks, and all three could be performed in parallel.

Figure 2. Task parallel decomposition example.

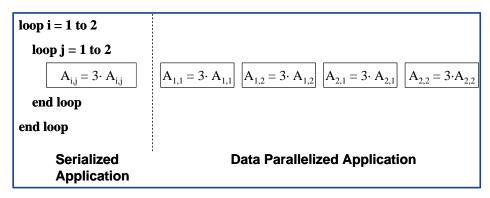

Data parallel decomposition is where the solution to a problem involves segmenting and decomposing major data structures (e.g., arrays) into smaller, independent blocks of data which can be processed

independently and concurrently from one another. An example of this form is a scalar multiplication operation on a matrix (Figure 3). In a serialized application, such operations are often performed sequentially through the aid of looping constructs. In this example, each cell can be operated on completely independent of other operations on other cells in the matrix. Furthermore, such operations can occur in any order and the resulting matrix from the operation will be the same in any case. The ordering imposed by the serial loop construct is simply artificial given the semantics of the loop construct; a parallelized form of this same matrix operation is not bound by such constraints. As such, each cell of the matrix could be the decomposed form of a parallelization effort. If the matrix is 2x2, then there could be four functions assigned to perform the scalar multiplication to each corresponding cell.

Figure 3. Data parallel decomposition example.

In task or data parallelization, it is often that one type will impact the other; in other words, task and data parallelism are not mutually exclusive. Most application problems are amenable to both forms of decomposition—knowing which form is the most appropriate can only be reasoned by thoroughly understanding the problem. Some problems, such as the image processing and capture application problem, are more amenable to task decomposition, whereas others (e.g. the scalar multiplication problem) are more amenable to data decomposition. In either type of parallelism, data structures must be designed so that the tasks from task parallel decomposition can perform their computations, or tasks must be created to manipulate the independent blocks of data resulting from the data parallel decomposition.

#### 3.4.3 Dependencies, Ordering, and Granularity

Dependencies can be in the form of either ordering between operations within the serialized application or data dependencies (e.g., shared memory) between operations. Some profiling tools can generate call graphs which can aid in discovering the ordering and the frequencies of operations and tasks within an application. The serialized form of the application may yield some insight into what that ordering will be, but some compromises may have been made to optimize the serialized application for a single core processor and that the ordering could be artificial to achieve other (prior) objectives. Having insight of the potential for parallelization of the application, separate from the

serialized form, may help identify false ordering (ordering which is not required) between operations and present opportunities for parallelization. In the image processing and capture application example above, counting the number of unique colors in the bitmap did not necessarily have to occur first.

Shared data dependencies between different (perhaps large) portions of code may also be discernible from call graphs, but it is more likely that inspection of the source code will be necessary to either confirm or refute such data dependencies. Static analysis tools and memory profiling tools may be available to aid in the identification of data dependencies for large regions of code (for example looking for access to global variables, shared memory regions, etc. across many lines of code or source code files). Such tools will likely be language dependent and possibly even platform dependent.

Hotspots that are the result of a computationally-intensive loop may create dependencies within an operation. These hotspots are candidates for parallelization because if the loop can be designed to be executed in parallel some speed-up can be achieved. However, in order to perform this activity, the loop must be analyzed and redesigned so that each loop iteration can be made independent—that is, each iteration can be safely executed in any order and any dependencies are not carried from each iteration. On the other hand, some loops used in serialized applications must have dependencies between iterations, such as performing accumulations or other associative operations which are more difficult to remove.

To identify speed-up and achieve efficient use of all the cores, the decomposition, ordering, design, and implementation of the tasks needed to perform the overall workload (task parallel or data parallel decomposition) must consider the target platform. This is to ensure that the work created for each of the tasks will be of sufficient size to keep the cores busy and be correctly balanced between the multiple cores. Previously, we illustrated in the prior scalar multiplication operation that a task could be created for each element of the matrix to perform the design operation. For this specific example, this would likely never be done here for various reasons:

- The allocation of a task for each cell of the matrix to one of the cores would simply not scale for a matrix of any practical size<sup>x</sup>

- The overhead introduced by parallelization would likely not outperform the serialized code

This underscores the point that determining the proper sizing (or granularity) of the tasks is non-trivial. For software engineers performing this activity for the first time, this might involve some trial and error after the parallelization of the application is shown to be correct. There are also heuristics which can aid in estimating granularity which may be available for the target platform, parallelization libraries, or languages used for the parallelization effort. For example, Thread Building Blocks<sup>xi</sup> recommends a "grainsize" (an indicator of granularity for the number of instructions to execute in the body of a task) of 10,000 to 100,000 instructions.

After conducting a parallelization exercise on the source code, revisit the assessment loop (Figure 1) to confirm that the expected results for speed-up occurred and that the regression test for the application passed.

#### 3.5 High-Level Design

After comprehending the algorithmic intent and serial implementation of a program, it is appropriate to begin the high-level design for a parallel implementation of the application. The intent of the high-level design phase is to partition the application into separate regions which expose work to run in parallel. Dependencies between regions will limit this parallelism. Additionally, characteristics of the target run time will practically limit the amount of work which can be done in parallel. Choose an appropriate granularity of decomposition which can be efficiently mapped onto the parallel run-time environment.

#### 3.5.1 Task Parallel Decomposition

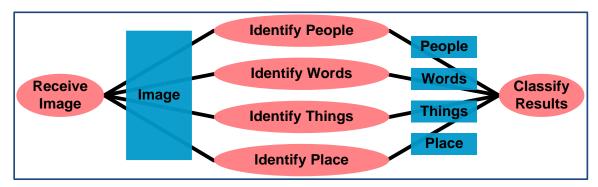

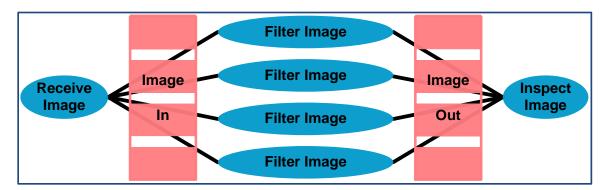

Task parallel decomposition enables different tasks to run in parallel. The different tasks may read shared data, but they produce independent results. In an example image recognition application (Figure 4), four separate identification tasks share the same input image data. Each task is specialized to identify different objects in the image. Once all four tasks have been completed, the aggregate data may be processed by downstream operations.

Figure 4. Task parallel image processing example.

For a given processing platform, the different 'identify' tasks may have different execution times. Though the four tasks may all be run in parallel, if identifying words, things, and places are each three times faster than identifying people, it may make sense to run the word, thing, and place identification tasks one after another in parallel with the slower people identification task. This type of load balancing is an example of how task parallel decomposition may need to be scheduled properly to most effectively utilize the available processing resources.

#### 3.5.2 Data Parallel Decomposition

Data parallel decomposition focuses on partitioning input data into separate regions and the same task is run in parallel on the different data regions. In another example image recognition application (Figure 5), each pixel in the output image is calculated using some corresponding combination of input pixels. An output pixel computation may share input pixels with its neighbors, but each output pixel can be computed independently of all others.

Figure 5. Data parallel image processing example.

Though each pixel may be computed in parallel, the granularity of decomposition must match the available resources. For example, if there are 8 logical processor cores available, the image could be sliced into 8 independent regions. Within a region, the pixels would be computed serially, but the regions themselves would all be computed in parallel. Data decomposition can inherently deliver a natural load balancing process. When the task being computed takes the same amount of time per pixel, which represents a static workload, then the data can be divided into equal segments to balance the load.

#### 3.5.3 Pipelined Decomposition

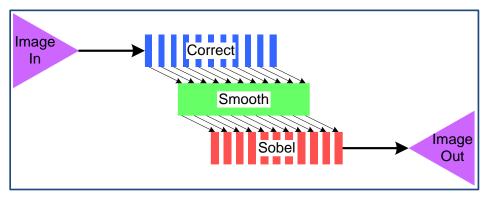

Pipelined decomposition may be considered a type of hybrid task-data decomposition whereby each task may be decomposed into separate functional stages. Each stage processes a subset of the overall data and passes its results to the next stage. Though each stage processes its data serially, all stages run in parallel to increase the processing throughput.

In an example imaging edge-detection application, it consists of a number of stages: pixel correction, image smoothing, and Sobel<sup>xii</sup> edge detection (Figure 6). With pipelined decomposition, a pixel block enters the pipeline at the correction stage and emerges after Sobel. As a data block moves from the first stage to the second, the next data block may enter the first stage. All three stages can run in parallel, each working on a different block of data at a different stage in the algorithm.

Figure 6. Pipelined edge detection

Ideally, pipeline decomposition requires the number of stages to be matched to the available processing resources. The overall throughput of the pipeline is also limited by the slowest pipeline stage. In the example above, the smoothing function requires the most work, and for each data block, the correction and Sobel functions must idle until the smoothing function completes. The smoothing function's speed determines the overall performance of the parallel implementation. Recursively parallelizing the smoothing function may shorten its execution time and better balance the pipeline.

#### 3.5.4 SIMD Processing

Most modern processors include some type of vector operations, termed single instruction, multiple data (SIMD) operations. A SIMD instruction enables the same operation to be applied to multiple data items in parallel. An example instruction might multiply four pairs of eight-bit data values, storing the result as four sixteen-bit data values. This type of low-level parallelism is often used within loops to increase the work per iteration. Where possible, this instruction-level parallelism should be applied first followed by the task level data decomposition previously discussed.

#### 3.5.5 Data Dependencies

When algorithms are implemented serially, there is a well-defined operation order which can be very inflexible. In the edge detection example, for a given data block, the Sobel cannot be computed until after the smoothing function completes. For other sets of operations, such as within the correction function, the order in which pixels are corrected may be irrelevant.

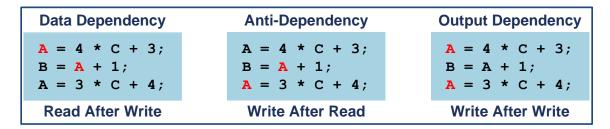

Dependencies between data reads and writes determine the partial order of computation. There are three types of data dependencies which limit the ordering: true data dependencies, anti-dependencies, and output dependencies (Figure 7).

Figure 7. Three types of data dependency examples (the dependencies are highlighted in red): a) data dependency; b) anti-dependency; and c) output dependency.

True data dependencies imply an ordering between operations in which a data value may not be read until after its value has been written. These are fundamental dependencies in an algorithm, although it might be possible to refactor algorithms to minimize the impact of this data dependency.

Anti-dependencies have the opposite relationship and can possibly be resolved by variable renaming. In an anti-dependency, a data value cannot be written until the previous data value has been read. In Figure 7b, the final assignment to A cannot occur before B is assigned, because B needs the previous value of A. In the final assignment, variable A is renamed to D, then the B and D assignments may be reordered.

Renaming may increase storage requirements when new variables are introduced if the lifetimes of the variables overlap as code is parallelized. Anti-dependencies are common occurrences in sequential code. For example, intermediate variables defined outside the loop may be used within each loop iteration. This is fine when operations occur sequentially. The same variable storage may be repeatedly reused. However, when using shared memory, if all iterations were run in parallel, they would be competing for the same shared intermediate variable space. One solution would be to have each iteration use its own local intermediate variables. Minimizing variable lifetimes through proper scoping helps to avoid these dependency types.

The third type of dependency is an output dependency. In an output dependency, writes to a variable may not be reordered if they change the final value of the variable that remains when the instructions are complete. In Figure 7c, the final assignment to A may not be moved above the first assignment, because the remaining value will not be correct.

Parallelizing an algorithm requires both honoring dependencies and appropriately matching the parallelism to the available resources. Algorithms with a high amount of data dependencies will not parallelize effectively. When all anti-dependencies are removed and still partitioning does not yield acceptable performance, consider changing algorithms to find an equivalent result using an algorithm which is more amenable to parallelism. This may not be possible when implementing a standard with strictly prescribed algorithms. In other cases, there may be effective ways to achieve similar results.

#### 3.6 Communication and Synchronization

Data dependencies establish a set of ordering requirements which must be enforced to ensure proper operation. Diverse parallel programming models use different techniques to ensure proper ordering.

#### 3.6.1 Shared Memory

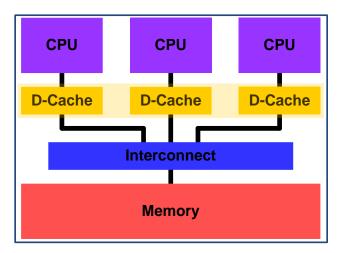

In a shared memory system, the individual processing units may locally cache memory, but the system must maintain a consistent view of shared memory between the processors (Figure 8). With caches, the silicon cost of maintaining a coherent view of memory can become very high if cache lines must be shared between processors. Proper data layout in memory can minimize this penalty.

Figure 8. Processing units share the same data memory.

Multiple threads of execution are used to run multiple tasks simultaneously. Data which is shared between tasks must also be properly synchronized by the developer in the application (i.e. locks) to ensure dependency relationships are properly maintained. In an example, threads T0 and T1 may both need to read and write variable 'A' (Figure 9). Without synchronization, the order of reads and writes between the two threads is unpredictable, and three different outcomes are possible.

Figure 9. Shared data synchronization.

Mutual exclusion through locks and semaphores is a common technique to ensure that only one thread at a time may execute code which encompasses certain critical dependencies. While one thread holds a lock for a critical section, other threads are blocked from entering, which if allowed, could violate dependencies involving data shared between the sections. In the example of Figure 9, properly locking the critical sections ensures that 'A' always receives 3 as a final value.

Generally, each processor runs one thread at a time. More threads may be created across the processor cores. When one thread blocks while waiting for the lock to clear, the operating system may wake up another ready thread to take its place.

The cost of acquiring and releasing a lock can be significant. Locks serialize code, so locking large critical sections will inhibit parallelism. On the other hand, using frequent, low-level locking may impose a large penalty for synchronization. The cost of creating and destroying completed tasks is also significant, so once again, the granularity of tasks and locking should match the available resources.

#### 3.6.2 Distributed Memory

With distributed memory systems, memory is not shared between systems and each processor manages its own local memory (Figure 10). Communication of data between tasks running on different processors is accomplished by sending and receiving data between them, often termed message-passing. While the thread programming model is appropriate for shared memory, the message passing model may be used with either distributed or shared memory systems.

In the distributed memory model, data must be *explicitly* shared between tasks. Synchronization between tasks can be achieved by synchronous send-receive semantics. A receiving task will block until the sending data is available. Alternatively, asynchronous send-receive semantics can be used where the receiving task can check or be notified when data is available without blocking. This permits overlap of computation and communication leading to significant performance gains.

Figure 10. Distributed memory architecture.

Relative to shared memory, distributed memory represents a higher overhead for communication, both in the setup and tear down of a message and in explicit copying of data, so message passing should be optimized for both functions.

#### 3.7 Load Balancing

The amount of work per computation may be fixed or it will depend on the input data. Work which is fixed, is termed a static workload, and may be partitioned during design time. Consider the edge detection example discussed previously. In data decomposition, the workload is the same for all pixels, and the parallelism scales easily across available processors.

What would happen if the run time of the smoothing function was dependent on the input data? For example, regions with slowly varying pixel values might take fewer compute cycles to smooth, while regions with rapidly changing pixel values might require extra processing. This type of workload varies dynamically depending on the pixel values - equally-sized pixel regions may contain very different workloads. Consider an image with widely varying pixels on the top half and a uniform color in the bottom half. If the work is split between two tasks, top and bottom and each running on separate processors, the bottom half will finish well in advance of the top half, and the bottom processor will idle.

With unpredictable workloads, the schedule can only be statistically optimized. In this case, dividing the work into smaller regions might improve the processing efficiency because the differences between neighboring workloads will be less. As the work is divided into smaller tasks, the cost of communication can become a significant portion of the task run time and must be considered in determining the best task sizes. Run times using thread pools or work stealing provide built-in support for dynamic load-balancing.

Task, data, and pipeline decompositions should always consider how to balance the workloads between regions. Static workloads are easy to analyze, while dynamic workloads will require

statistical considerations to find a good level of granularity which both matches the available resources and alleviates the workload mismatches.

#### 3.8 Decomposition Approaches

The high-level design process decomposes the algorithm into separate processing regions, taking the data dependencies, communication, and synchronization requirements into consideration, and then performs load balancing to establish an efficient partitioning for implementation.

#### 3.8.1 Top-Down or Bottoms-Up

There are two main approaches to decompose an algorithm - top-down and bottom-up. In a top-down approach, the algorithm is decomposed into separate regions. Some regions will remain serial, while other regions may be decomposed using task, data, and pipelined decompositions. Use profiling information from high-level analysis to identify the most beneficial regions to be decomposed. After each decomposition effort, the parallel performance can be estimated. If not enough performance is achieved, then regions can be further subdivided trying to find additional parallelism.

Some regions will easily decompose into many fine-grained regions, and there will be a tradeoff of granularity and overhead. Data decomposing an image into pixels might be an extreme example of fine-grained implementation. The number of available cores, overhead of creating and destroying tasks, and communication and synchronization overhead become a significant cost.

As we described previously, profiling information from high-level analysis identifies the most important hot spot regions. To gain the most benefit, concentrate on parallelizing the hot spots that consume relatively large amounts of execution time. A true bottom-up approach will start with the finest grained partitioning for hot spot regions and progressively move up to encompass larger regions, maintaining a balance between partitioning and overhead. Once a suitable granularity is established, a larger region can be assembled in parallel from the smaller regions until achieving a satisfactory estimated performance level.

#### 3.8.2 Hybrid Decomposition

Decompositions may be applied hierarchically to best match the available and type of processing resources. For example, consider a two-stage pipeline decomposition in which the first stage is 6 times slower than the second (Figure 11). Therefore, the initial pipeline decomposition will focus on the slower first stage.

Using data decomposition and assuming sufficient processing resources, it may be possible to move six data blocks in parallel through the first stage, which can then run serially through the second stage in the same amount of time, effectively balancing the pipeline and optimizing the throughput.

Figure 11. Example depicts 2-stage pipeline combining data and pipeline decomposition.

#### 3.9 Parallel Design in Modeling

In some application areas, it may be necessary to undertake the analysis and high-level design of parallelism in the modeling phase because algorithms are designed on special modeling tools that automatically generate C code. For example, in recent control systems, mathematical modeling tools such as MATLAB/Simulink® are utilized. Owing to the use of these tools, Model-Based Development (MBD) has become prevalent, wherein algorithms are designed and simulated using the modeling tools, and implementation is performed with the automatically generated code by using these tools. In this design flow, given that high-level design and analysis with automatically generated code are sometimes futile, it is indispensable to design parallelism in modeling.

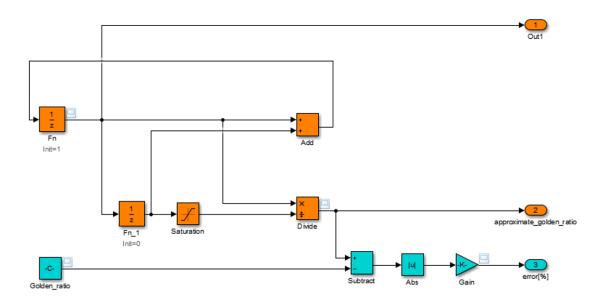

Model-Based Parallelization (MBP) can be used for this purpose. In many modeling tools, data flow block diagrams are utilized to represent models. Figure 12 shows an example of Simulink model for the Fibonacci function ( $f_{n+1} = f_n + f_{n-1}$ ) and comparison of  $f_n/f_{n-1}$  with its convergence value, with is also called the golden ratio. In this diagram, the blocks marked by 1/z are unit delays that keep values of  $f_n$  and  $f_{n-1}$ . At each step, the calculation initializes with the reading of the values of  $f_n$  and  $f_{n-1}$  at the unit delays marked (S). Then, the values of  $f_{n+1}$  and  $f_n$  at the unit delays marked (T) and the calculated values at output ports marked (T) are stored and outputted. The diagram explicitly shows data dependency; task parallel decomposition creates a model partitioning problem, which considers load balancing, inter-core communication, and computation orders with start and end points (Figure 13). In addition, there is a way to draw data parallelism using special blocks such as "For Iterator" blocks in Simulink. Therefore, MBP might be useful for the analysis and high-level design of parallelism in modeling.

Figure 12. Model for Fibonacci function

Figure 13. Model partitioning.

# CHAPTER 4: IMPLEMENTATION AND LOW-LEVEL DESIGN

#### 4.1 Introduction

Parallel implementations are highly platform architecture dependent. For a set of representative architectures, this chapter discusses the choice of parallel implementation technology (such as threading or message-passing) and recommended implementation techniques (such as incremental refinement and serial consistency). Good implementations properly realize high-level design metrics, ease debugging, and reduce latent bugs.

#### 4.2 Thread Based Implementations