Multicore

# Software-Hardware Interface for Multi-Many-Core (SHIM) Specification V1.00 Final

Document ID: SHIM Specification

Document Version: 1.00

Status: Final

Copyright © 2015 The Multicore Association, Inc.

All rights reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission from The Multicore Association, Inc.

All copyright, confidential information, patents, design rights and all other intellectual property rights of whatsoever nature contained herein are and shall remain the sole and exclusive property of Multicore Association. The information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by The Multicore Association, Inc. for its use, or for any infringements of patents or other rights of third parties resulting from its use.

The Multicore Association, Inc. name and The Multicore Association, Inc. logo are trademarks or registered trademarks of The Multicore Association, Inc. All other trademarks are the property of their respective owners.

The Multicore Association, Inc. PO Box 4854 El Dorado Hills, CA 95762 530-672-9113 www.multicore-association.org

# **Table of Contents**

| Pre | eface   |                                                   | 6  |

|-----|---------|---------------------------------------------------|----|

|     | Definit | itions                                            | 6  |

| 1.  | Introd  | duction                                           | 7  |

|     | 1.1     | Overview                                          | 7  |

|     | 1.2     | Interface                                         |    |

|     | 1.3     | SHIM Editor                                       | 9  |

| 2.  | SHIM    | Concepts                                          | 12 |

|     | 2.1     | Topology - ComponentSet                           | 12 |

|     | 2.2     | Memory - AddressSpaceSet                          |    |

|     | 2.3     | Inter-core communication – CommunicationSet       |    |

|     | 2.4     | Performance                                       |    |

|     |         | 2.4.1 General                                     |    |

|     |         | 2.4.2 Latency and Pitch                           |    |

|     |         | 2.4.3 Using triplets                              |    |

|     | 2.5     | Software View - what is in and what is not        |    |

|     | 2.6     | XML                                               |    |

|     |         | 2.6.1 Data Binding                                |    |

|     | 07      | 2.6.2 Who Creates SHIM XML                        |    |

|     | 2.7     | Configuration<br>2.7.1 General                    |    |

|     |         | 2.7.1 General                                     |    |

|     | 2.8     | Reference Authoring Tools                         |    |

|     | 2.0     | Roadmap                                           |    |

|     | 2.0     | 2.9.1 Componentization of SHIM XML                |    |

|     |         | 2.9.2 Hardware-Related Software Properties        |    |

|     |         | 2.9.3 Schema Refinement for Smaller XML           |    |

| 3.  | SHIM    | Interface                                         | 22 |

|     | 3.1     | shim.xsd                                          |    |

|     | 3.2     | Conventions                                       |    |

|     | 3.3     | Enumeration                                       | 29 |

|     | 3.4     | SystemConfiguration                               |    |

|     |         | 3.4.1 ClockFrequency                              |    |

|     | 3.5     | ComponentSet                                      | 32 |

|     |         | 3.5.1 MasterComponent                             |    |

|     |         | 3.5.2 SlaveComponent                              |    |

|     |         | 3.5.3 Cache                                       |    |

|     |         | 3.5.4 AccessTypeSet                               |    |

|     |         | 3.5.5 AccessType                                  |    |

|     |         | 3.5.6     CommonInstructionSet                    |    |

|     |         | 3.5.7     Instruction       3.5.8     Performance |    |

|     |         | 3.5.9 Latency                                     |    |

|     |         | 3.5.10 Pitch                                      |    |

|     | 3.6     | AddressSpaceSet                                   |    |

|     | 2.2     | 3.6.1 AddressSpace                                |    |

|     |         | 3.6.2 SubSpace                                    |    |

|     |         | 3.6.3 MemoryConsistencyModel                      |    |

|     |         | 3.6.4 MasterŚlaveBindingSet                       |    |

|     |         | 3.6.5 MasterSlaveBinding                          |    |

|     |         |                                                   |    |

|     |         | 3.6.6 Accessor<br>3.6.7 PerformanceSet            |    |

|    | 3.7                                       | CommunicationSet                                               | 41 |  |  |  |  |

|----|-------------------------------------------|----------------------------------------------------------------|----|--|--|--|--|

|    |                                           | 3.7.1 FIFOCommunication                                        | 41 |  |  |  |  |

|    |                                           | 3.7.2 SharedRegisterCommunication                              | 42 |  |  |  |  |

|    |                                           | 3.7.3 InterruptCommunication                                   | 42 |  |  |  |  |

|    |                                           | 3.7.4 Shared Memory Communication                              | 43 |  |  |  |  |

|    |                                           | 3.7.5 EventCommunication                                       |    |  |  |  |  |

|    |                                           | 3.7.6 ConnectionSet                                            |    |  |  |  |  |

|    |                                           | 3.7.7 Connection                                               |    |  |  |  |  |

| 4. | Use C                                     | Cases                                                          |    |  |  |  |  |

|    | 4.1                                       | Performance Estimation: Auto-Parallelizing Compiler            | 45 |  |  |  |  |

|    | 4.1                                       | 4.1.1 Using "CommonInstructionSet"                             |    |  |  |  |  |

|    |                                           | 4.1.2 Using "PerformanceSet"                                   |    |  |  |  |  |

|    |                                           |                                                                |    |  |  |  |  |

|    |                                           |                                                                |    |  |  |  |  |

|    | 10                                        | 4.1.4 Using "FIFOCommunication"                                |    |  |  |  |  |

|    | 4.2                                       | Tool Configuration - RTOS Configuration Tool                   |    |  |  |  |  |

|    |                                           | 4.2.1 Using "ClockFrequency"                                   |    |  |  |  |  |

|    |                                           | 4.2.2 Using "SubSpace"                                         |    |  |  |  |  |

|    | 4.3                                       | Hardware Modeling                                              | 47 |  |  |  |  |

| 5. | SHIM                                      | XML Authoring Rules and Guidelines                             | 48 |  |  |  |  |

|    | 5.1                                       | File Name [Rule]                                               | 48 |  |  |  |  |

|    | 5.2                                       | Naming of Various Objects [Rule]                               |    |  |  |  |  |

|    | 5.3                                       | Level of Detail and Precision [Guideline]                      |    |  |  |  |  |

| ~  |                                           | non Configuration File (CCF)                                   |    |  |  |  |  |

| 6. |                                           |                                                                |    |  |  |  |  |

|    | 6.1                                       | Concept                                                        |    |  |  |  |  |

|    |                                           | 6.1.1 Multiple Hardware Configuration                          |    |  |  |  |  |

|    |                                           | 6.1.2 Vendor-Specific Hardware Features Affecting SHIM Objects |    |  |  |  |  |

|    |                                           | 6.1.3 Configuration Tool User Interface                        |    |  |  |  |  |

|    | 6.2                                       | Interface                                                      |    |  |  |  |  |

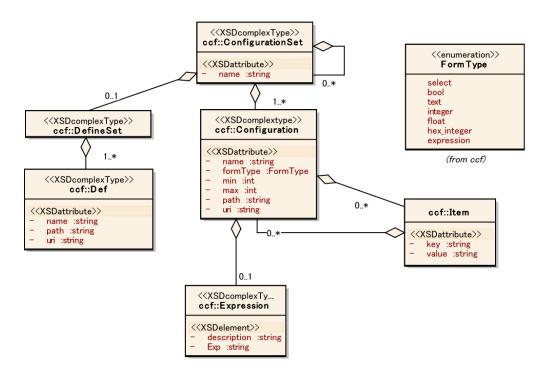

|    |                                           | 6.2.1 XML Schema                                               | 51 |  |  |  |  |

|    |                                           | 6.2.2 Semantics                                                | 53 |  |  |  |  |

|    |                                           | 6.2.3 FormType                                                 | 53 |  |  |  |  |

|    |                                           | 6.2.4 ConfigurationSet                                         | 53 |  |  |  |  |

|    |                                           | 6.2.5 Configuration                                            | 54 |  |  |  |  |

|    |                                           | 6.2.6 Item                                                     |    |  |  |  |  |

|    |                                           | 6.2.7 Expression                                               |    |  |  |  |  |

|    |                                           | 6.2.8 Def                                                      |    |  |  |  |  |

|    | 6.3                                       | Examples                                                       |    |  |  |  |  |

|    | 0.0                                       | 6.3.1 Generic                                                  |    |  |  |  |  |

|    |                                           | 6.3.2 Nested configuration                                     |    |  |  |  |  |

| 7. | FAO                                       |                                                                |    |  |  |  |  |

|    |                                           |                                                                |    |  |  |  |  |

| 8. | Арреі                                     | ndix A: Acknowledgements                                       |    |  |  |  |  |

|    |                                           |                                                                |    |  |  |  |  |

| T۵ | BIF 1.9                                   | SHIM REPRESENTATION OF HARDWARE COMPONENTS                     | 12 |  |  |  |  |

|    |                                           | NTER-CORE COMMUNICATION CLASSES                                |    |  |  |  |  |

| -  | TABLE 2. INTER-CORE COMMUNICATION CLASSES |                                                                |    |  |  |  |  |

| TABLE Z. INTER-CORE COMMUNICATION CLASSES                                            |   |

|--------------------------------------------------------------------------------------|---|

| TABLE 3. PERFORMANCE PROPERTIES IN SHIM                                              |   |

| TABLE 4. USING TRIPLES.                                                              |   |

| TABLE 5. PERFORMANCE ESTIMATION USE CASE.                                            |   |

| TABLE 6. TOOL CONFIGURATION USE CASE                                                 |   |

| TABLE 7. HARDWARE MODELING USE CASE                                                  |   |

|                                                                                      |   |

| FIGURE 4. CLIIM PROVIDED THE INTEREASE RETRIENT THE HARRING AND THE COST MARE TOOLO. | - |

| FIGURE 3. CLASS DIAGRAM REPRESENTATION OF THE WHOLE SHIM XML SCHEMA           | 10 |

|-------------------------------------------------------------------------------|----|

| FIGURE 4. SHIM XML FILE EXAMPLE                                               | 11 |

| FIGURE 5. SHIM EDITOR MAIN WINDOW                                             | 11 |

| FIGURE 6. LATENCY AND PITCH REPRESENT THE PRIMARY PERFORMANCE CHARACTERISTICS | 15 |

| FIGURE 7. CCF EXAMPLE                                                         | 19 |

| FIGURE 8. GUI GENERATED BY CCF                                                | 20 |

| FIGURE 9. COMMON CONFIGURATION FILE (CCF) CLASS DIAGRAM                       | 51 |

# Preface

This document is intended primarily for tool developers and hardware developers who would use SHIM to exchange hardware description for software tools. It also attempts to provide software developers with insights into what hardware information is described in SHIM to foster understanding of the intention and the extent of SHIM.

This document begins with the introduction to SHIM, providing the background, the overall concept, and model. It is followed by a chapter detailing the concept of SHIM, such as the purpose, scope, design, interface, limitation, providing the basic idea why SHIM is as specified in this document, and also trying to explain the basic principles for future extension of the specification. A chapter describing the interface follows, which is a description of SHIM XML schema and APIs that are mostly derived directly from the schema via XML data binding technique. A chapter providing some of the detailed use cases follows, allowing the reader to gain insights into how SHIM can be used in action. Finally, this document ends with various Appendixes providing further detailed information.

# Definitions

All new terms are defined at the first appearance, either in the main text body or as a footnote.

# 1. Introduction

# 1.1 **Overview**

Multicore processors have become the norm, and processors with tens, and even more than a hundred cores are emerging. These multicore processors vary not only in the number of cores, but also in inter-connects, cluster organization, and memory systems (including hierarchy and cache coherency), among others. While the trend for an increasing number of cores is both natural and unavoidable from a processor design perspective, this poses tremendous challenges to the software developers to cope with the significant hardware variance, while bearing a burden to re-use the existing and newly created software for different hardware. Moreover, all this must occur while achieving the performance expected from the multicore processors, which requires deep understanding of the specific multicore architecture. Various tools, such as auto-parallelizing compilers, parallelization tools, OS/middleware configurators, and performance analysis tools, aid developers to design, implement, and analyze the software. However, these tools must comprehend the complex multicore processor, transferring the burden to the tool developers. Therefore, it is critical to lower the cost of supporting new multicore hardware by various tools, but there has been a lack of effort in academia or industry to solve these issues, thereby hindering the development of the multicore tool eco-system.

The SHIM, Software-Hardware Interface for Multi-many-core, is a joint industrial and academic effort to standardize the interface between the multicore hardware and the software tools. As a result, we aim to lower the cost of supporting new multicore hardware using the standard interface. This will encourage the development of new innovative multicore tools, resulting in a richer eco-system of multicore technologies, which in turn should benefit system developers, semiconductor vendors, and tool vendors.

# 1.2 Interface

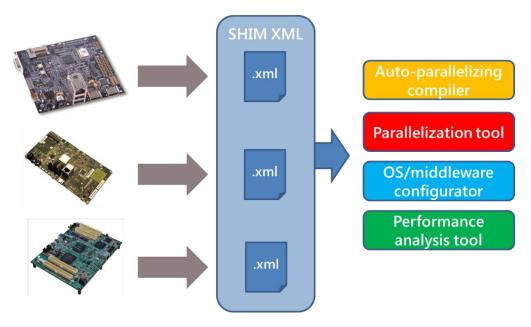

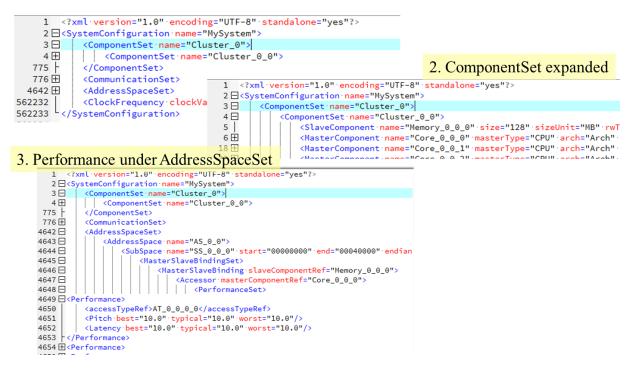

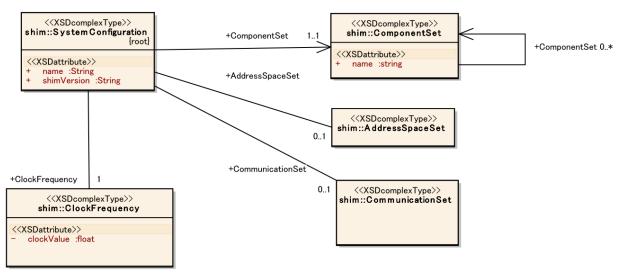

The SHIM is defined as an XML schema. A multicore hardware implementation is expressed as a SHIM XML file which can be used by various tools (Figure 1).

Figure 1. SHIM provides the interface between the hardware and the software tools

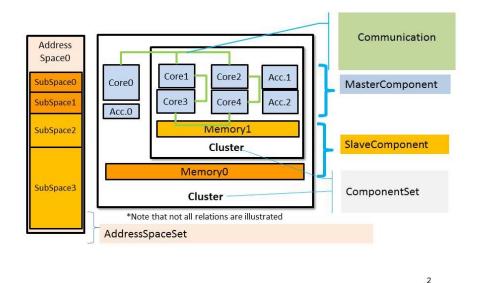

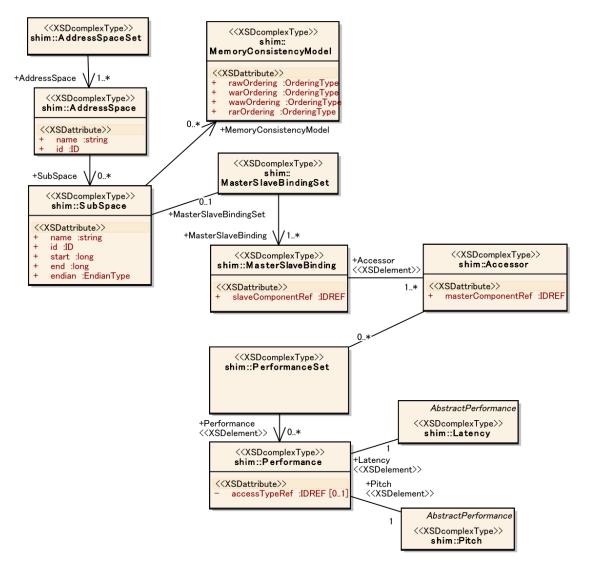

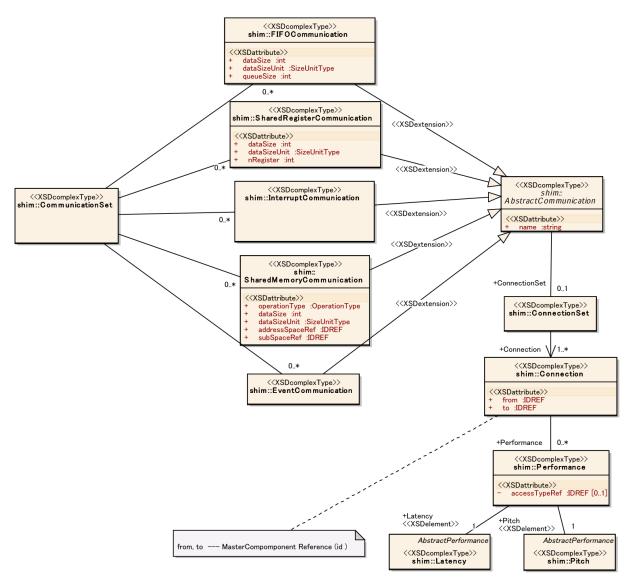

The SHIM XML file has a tree structure (Figure 4. SHIM XML file example) with three top level components, namely *ComponentSet*, "AddressSpaceSet, and *CommunicationSet*, each containing further child elements. The *ComponentSet* contains *MasterComponent* (representing a processor or accelerator) and *SlaveComponent* (representing a memory block or memory subsystem). The *AddressSpaceSet* contains one or more *AddressSpace*, which in turn contains *SubSpace*. Finally the *CommunicationSet* contains any number of *Communication* elements, describing the connection and communication between a pair of *MasterComponents*.

#### Figure 2. The SHIM elements mapped to a pseudo-multicore hardware

A *ComponentSet* can nest itself. For example, it can be used to express a chip that contains multiple hardware clusters, each cluster containing multiple cores with a cluster local memory. It can also be used to describe a board, which in turn may contain one or more multicore chips. A *ComponentSet* can even be used to describe a system with multiple boards, each board connected via PCI Express, for example. As such, the *ComponentSet* tree describes the multicore hardware system topology. This topological architectural information is important for software tools to be able to identify the number of cores, location of the memory devices, and how cores are organized into different clusters.

Since SHIM is for software tools, it is essential to understand from a software perspective, the connection and communication mechanism between the cores (including accelerators), as well as how these cores can access the different memories. The former is described as *CommunicationSet* containing different communication classes. A simple example of defined classes is *InterruptCommunication*, which contains one or more "connection" class, which binds a pair of *MasterComponents*. For memory access, the *SubSpace* containing references to a *MasterComponent* and *SlaveComponent*, describing which core/accelerator can access which memory through the address range.

The hardware architectural information described so far allows tools to understand the hardware topology, and how the cores and memory devices are connected. However, this alone is often insufficient for many tools, since the application software supported by these tools must not just 'run', but run with performance qualifiers. To achieve this, the tools must 'estimate' the rough performance so that the system designers and software developers know the expected performance from the given application and multicore hardware. Therefore, SHIM, in addition to the hardware topological information, describes the performance properties associated with the processor cycles consumed to perform the various core-to-core communication (*CommunicationSet*) and also the memory access cycles by different cores and accelerators. The performance is described as *Performance* element, which contains *Latency* and *Pitch*, expressed in processor cycles. The *Performance* element exists for each *CommunicationSet*, for each specific pair of two *MasterComponents*. For memory access performance, for each *MasterSlaveBinding* of each *SubSpace*, and for each *AccessType*, which are defined for each *MasterComponent*, a specific *Performance* element is included. So for each different access type (e.g., read or write, word access or double word access), a different *Performance* element is provided. The cycles can be described in a form of triplet, which are 'best', 'typical', and 'worst', to accommodate the possible performance variance. The tool must be intelligent enough to benefit from these figures, such as analyzing the application code if it is issuing a sequential memory access, which generally falls into use of the 'best' cycles. Note that the cycles mentioned here are processor-cycles, and *ClockFrequency* of *MasterComponent* overrides that of *SystemConfiguration* if they are not identical.

# 1.3 SHIM Editor

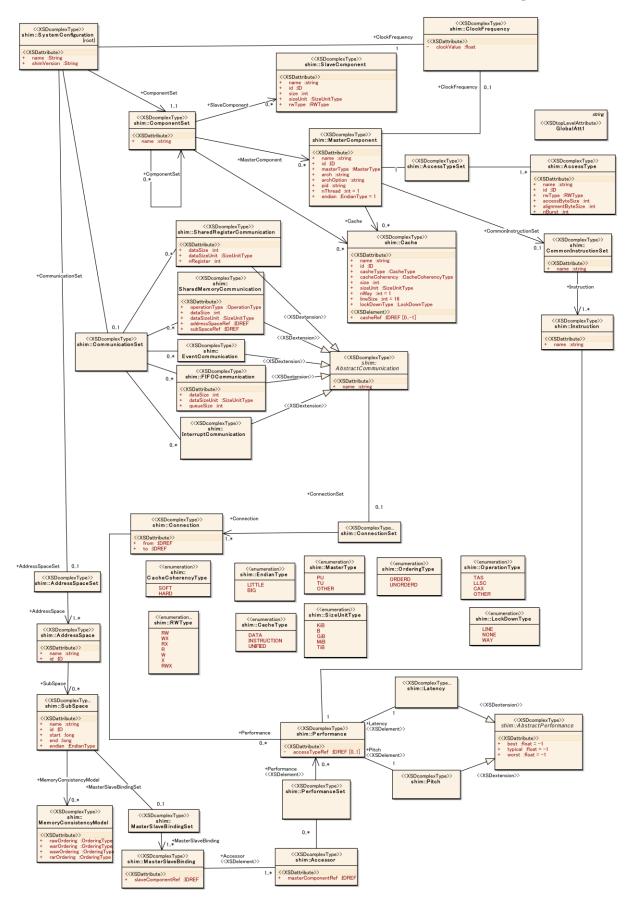

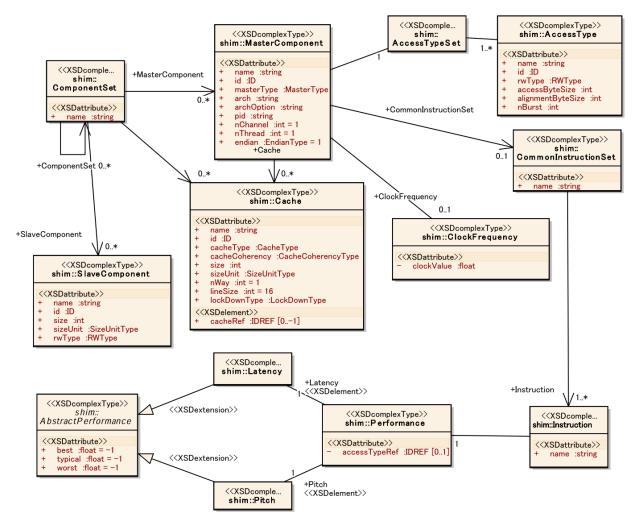

Although a SHIM XML schema is relatively simple, as can be seen on the UML Class diagram representation of the whole SHIM XML schema (Figure 3), the resulting SHIM XML file can be quite large, mostly due to all the *Performance* element descriptions for all types of memory accesses. Writing it manually can be tedious and errorprone, so we have developed an editor tool called the SHIM Editor, to foster authoring a SHIM XML file. The generated SHIM XML file is shown in Figure 4, and the SHIM Editor prototype's main window is shown in Figure 5.

Figure 3. Class diagram representation of the whole SHIM XML schema

### 1. All root elements

Figure 4. SHIM XML file example

| SHIM Editor                                |                                                                       |            |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------|------------|--|--|--|

| File Preferences Help                      |                                                                       |            |  |  |  |

| Open New Re-Make AddressSpaceSet Re-Make   | Open New Re-Make AddressSpaceSet Re-Make CommunicaionSet ElementTable |            |  |  |  |

| System Components AddressSpace Communi     | ications                                                              |            |  |  |  |

| ComponentSetTree Master Component          |                                                                       |            |  |  |  |

| ▲ [CS] Cluster_0                           | Name                                                                  | Core_0_0_0 |  |  |  |

| ▲ [CS] Cluster_0_0                         | Туре                                                                  | PU 🔹       |  |  |  |

| [MC] Core_0_0_0                            | Type                                                                  |            |  |  |  |

| UnifiedCache_0_0_0                         | Arch                                                                  | Generic    |  |  |  |

| AccessTypeSet                              | ArchOption                                                            |            |  |  |  |

| [CommonInstructionSet]LLVM InstructionSet] | Pid                                                                   | 0          |  |  |  |

| ClockFrequency                             | Più                                                                   | 0          |  |  |  |

| ▷ [MC] Core_0_0_1                          | nThread                                                               | 1          |  |  |  |

| [MC] Core_0_0_2                            | Endian                                                                |            |  |  |  |

| [MC] Core_0_3                              |                                                                       |            |  |  |  |

| [SC] Memory_0_0_0                          |                                                                       |            |  |  |  |

| [SC] Memory_0_0_1                          |                                                                       |            |  |  |  |

| [SC] Memory_0_0_2                          |                                                                       |            |  |  |  |

| [CS] Cluster_0_1                           |                                                                       |            |  |  |  |

| [MC] Core_0_1_0                            | J                                                                     |            |  |  |  |

| [MC] Core_0_1_1                            |                                                                       |            |  |  |  |

| [MC] Core_0_1_2                            |                                                                       |            |  |  |  |

| ▷ [MC] Core_0_1_3                          |                                                                       |            |  |  |  |

| ۰                                          |                                                                       |            |  |  |  |

| Re-number nodes                            | Apply                                                                 |            |  |  |  |

|                                            |                                                                       |            |  |  |  |

|                                            |                                                                       |            |  |  |  |

Figure 5. SHIM Editor main window

# 2. SHIM Concepts

This section describes the major SHIM concepts, providing the basic idea why SHIM is as specified in this document, and also attempts to indicate the principle for future extension of the specification. This chapter should provide a foundation for understanding the <u>SHIM interface</u>, so it is strongly recommended to read this thoroughly before diving into the interface details.

# 2.1 **Topology - ComponentSet**

A simple hardware setup may consist of a single processor core and a single memory – however, the multi-manycore hardware has multiple processor cores and memory devices of various types in various configurations. The combination and configuration of processor and memory characterizes the multi-many-core hardware, and it is essential for software tools to comprehend them.

SHIM expresses the particular mix of processors and memory devices as 'topology'. In the electrical circuits' terminology, topology "*is the form taken by the network of interconnections of the circuit components. Different specific values or ratings of the components are regarded as being the same topology. Topology is not concerned with the physical layout of components in a circuit, nor with their positions on a circuit diagram. It is only concerned with what connections exist between the components. There may be numerous physical layouts and circuit diagrams that all amount to the same topology<sup>1</sup>." From the SHIM's perspective, the topology is extended further. In addition to processor cores and memory devices, which are components in the electrical terminology, we also include '<i>clusters*', which is a particular set or grouping of processor cores and memory devices. Usually there are electrical connections between a cluster and other hardware elements, however SHIM does not necessarily deal with actual electrical connections, so the cluster may not form any connection. However, it is critical for software tools to see how processor cores and memory devices are grouped as it is often an indication of a performance difference, therefore SHIM includes *cluster* as a part of its topological expression.

A *cluster* is composed of any combination of another (inner) cluster, processor core, and memory device. SHIM has its own way of classifying and naming these objects (Table 1). A processor core is represented as a *MasterComponent* object. As can be seen from the table, a *MasterComponent* can also be some type of accelerator (e.g., a DMA controller). The objective of MasterComponent is to represent those electrical components that play the role of master component in the traditional master-slave bus setup, but only if they are relevant to the software view SHIM defines.

| SHIM term       | Hardware term                                                    |

|-----------------|------------------------------------------------------------------|

| ComponentSet    | Cluster of any level (a hardware board itself is also a cluster) |

| MasterComponent | Processor core, accelerator, or other master devices             |

| SlaveComponent  | Memory                                                           |

### Table 1. SHIM representation of hardware components

The *cluster*, or *ComponentSet*, can be used to express not only a processor core cluster, but also a hardware board. It can also be extrapolated to represent a system composed of multiple boards – in this case, the outermost cluster is the system boundary itself.

# 2.2 Memory - AddressSpaceSet

A software program accesses memory through a logical window called the address space. Processor hardware usually supports multiple address spaces, for different access privileges, for example. An address space is further

<sup>&</sup>lt;sup>1</sup> <u>http://en.wikipedia.org/wiki/Topology\_(electronics)</u>

subdivided into multiple subspaces, or address blocks. When a program makes an access somewhere in a memory device, it performs this by issuing a load or store instruction with its source or destination address falling into any one of the subspaces. To accommodate this memory setup, SHIM has a group of objects called *AddressSpaceSet*. An *AddressSpaceSet* can contain multiple *AddressSpace*, and each *AddressSpace* can contain multiple *SubSpace*.

A *SubSpace* is mapped to a physical memory device, or *SlaveComponent*, residing in some cluster, or *ComponentSet*. To describe the binding for which *SlaveComponent* is mapped to a specific *SubSpace*, the SHIM specification uses an object called *MasterSlaveBinding*. The object describes the mapping between a memory device and a memory subspace; it also indicates which *MasterComponent* (e.g., a processor core) has access to the memory. Since it is possible for multiple *MasterComponents* to have access to a memory *SubSpace*, a set object called *MasterSlaveBindingSet* is also defined to group multiple *MasterSlaveBinding* objects.

By exploring the objects under the *AddressSpaceSet*, a tool can discover what memory spaces are available and which processor core or accelerator has what kind of access to those. Multiple *AdddressSpace/SubSpace* may share the same *SlaveComponent*. If the sharing occurs for only parts of the physical memory, it can be divided into multiple *SlaveComponents*.

# 2.3 Inter-core communication – CommunicationSet

For software to run on multiple processor cores and accelerators with some degree of cooperative manner, it often exchanges data, which may be available via a shared memory region. The software must also trigger, synchronize, or perform mutual exclusion in some way. In cases where shared memory is not available, some form of core-to-core or *MasterComponent* to *MasterComponent* communications is required. To accommodate this situation, SHIM defines a class of objects called *CommunicationSet*. All SHIM objects have a child object called *ConnectionSet*, which includes one or more *Connection* that describes the source and destination *MasterComponents* for the communication. The variety of *ConnectionSet* classes have similar communication mechanisms (Table 2).

| CommunicationSet classes    | Description                                                                                                                                                                                                                                       |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SharedRegisterCommunication | Shared register based communication. Often such hardware provides a set of registers that can be accessed by multiple processor cores.                                                                                                            |

| SharedMemoryCommunication   | Shared memory based communications. An operation type is specified from TAS (Test and set), LLSC (Load-link/Store conditional), CAX (Compare and exchange), and OTHER (other unspecified operation).                                              |

| EventCommunication          | An event is often a register bitmap based communication – if a processor core raises an event (Boolean), that is sent to another core and can be seen as the mapped event signaled in its event register. It may or may not trigger an interrupt. |

| FIFOCommunication           | A FIFO is sometimes used for inter-core communication and often<br>implemented as FIFO registers, possibly with buffers of varying depth.                                                                                                         |

| InterruptCommunication      | This is a typical inter-processor-interrupt. This object only has the <i>ConnectionSet</i> .                                                                                                                                                      |

Each class has its unique properties or attributes. All classes include connection information describing which pairs of cores are connected by the particular communication object. Since there can be multiple connections, the object contains *ConnectionSet*, which in turn contains any number of *Connection*. Each *Connection* contains references to a pair of *MasterComponents*.

Software tools can use this information to obtain the type of *MasterComponent*-to-*MasterComponent* communication mechanisms are supported by a particular hardware implementation represented by a SHIM XML. Note that the connection can be across multiple *ComponentSet* boundaries, even if it traverses the chip or hardware board boundaries.

# 2.4 **Performance**

### 2.4.1 General

As expected, different processor hardware has different performance characteristics. The performance characteristics can be very complex for a multi-many-core hardware and will have tremendous impact on the software design. Since SHIM's principle is to capture the properties that affect the software at the architectural design level, it is intrinsic to include such performance properties (Table 3).

| Performance Property        | Related SHIM Object                                      | Description                                                                                                                                                                                                  |  |

|-----------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction execution       | CommonInstructionSet,<br>Instruction                     | The execution cycles of processor instructions. The instruction set is described as LLVM IR, and the cycles of a particular processor architecture is expressed in terms of these LLVM IR instructions.      |  |

| Memory access               | SubSpace,<br>MasterSlaveBinding,<br>Accessor, AccessType | The processor cycles for accessing a memory. Each<br>processor core can have different cycles for different<br>access types such as read or write and accessing by<br>byte, word, double word accesses, etc. |  |

| Inter-core<br>communication | CommunicationSet classes                                 | The time needed for a particular connection of two <i>MasterComponent</i> for a particular <i>Communication</i> class, such as <i>InterruptCommunication</i> , in processor cycles.                          |  |

### Table 3. Performance properties in SHIM

There are significant performance variations among different processor, memory, and inter-connect architectures, so all performance properties are expressed as a triplet of best, typical, and worst cycles. Some architectures are highly deterministic and may have little variation in the performance of some operations; this will be depicted with the triplet bearing similar, if not the same, values. The software tool can use this information to determine the hardware dynamism or determinism by examining the deviation in the values. For such hardware, the estimation based on SHIM XML can be highly accurate, well under the 20% error rate that SHIM targets (even possibly nearing single digits of error percentage). Some hardware could have fairly dynamic performance characteristics, performing some operations mostly in two cycles, and possibly in 200 cycles in some cases, for example. This dynamic behavior often is derived from a wide range of speculative and probabilistic algorithms employed by modern hardware; this 'best-effort' approach as opposed to a 'guarantee' approach is quite popular and the trend continues.

SHIM, as said in <u>Software View - what is in and what is not</u>, provides software with a simpler view of the underlying hardware and it avoids descriptions of what speculative algorithm is supported and its detailed spec. The triplet performance representation provides a window to adapt the dynamism by carefully setting up the three values, encapsulating the various hardware mechanism underneath. After all, it is technically infeasible, if not impossible, to achieve 100% accuracy in the hardware performance estimation – the idea is to obtain accurate enough performance estimation for system architectural design – the rest must be optimized in the later phase of system development. This approach is reasonable since the final set of software is unavailable before the system development stage and there are many other factors that influence the development, and thus the design, as the project progresses.

SHIM.xml is created for a specific hardware (and system software if necessary) configuration. If, for example, quality of service (QoS) is to impact the performance characteristics at a level greater than the goal of 20% error rate, multiple SHIM XML files must be authored or a <u>Common Configuration File (CCF)</u> must be used to describe the variation in performance.

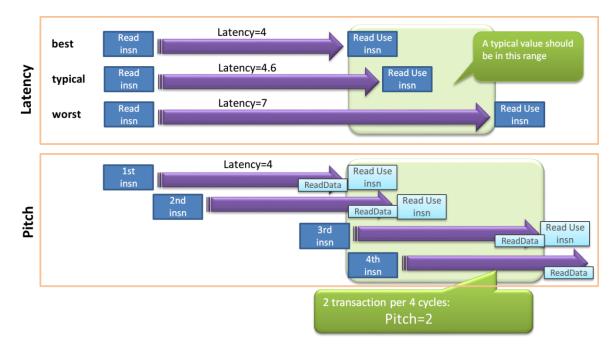

# 2.4.2 Latency and Pitch

The performance object is characterized by a pair of triplets - one associated with 'latency', the other for the 'pitch' (Figure 6). The latency, or *Latency* in terms of SHIM class, is specifically the processor cycles for performing the particular operation. The *Pitch* is a trickier process – it is the size of stride when executing the operation in consecutive manner, also expressed in processor cycles. As indicated previously, modern hardware has a mechanism to speculate what would be the next software action. When accessing a memory, for example, the hardware has a cache that reads the memory in its line size, even if a smaller size of memory is requested by a particular 'load' instruction. In essence, it can read the next memory address ahead of time, hoping the next 'load' instruction will follow at the consecutive address (called a speculative fetch). If that fetch proves true, the next read operation can complete by reading from the cache, without actually accessing the slower main memory. The hardware supports other similar mechanisms – all trying to take advantage of repetitive software behavior. This action results in the performance characteristics that, if the similar operation is performed repeatedly in some way, the average execution cycles per operation are less than it would be if it is not. The *Pitch* is specifically meant to describe this performance property.

### Figure 6. Latency and Pitch represent the primary performance characteristics.

The software tool's job is to see if a particular operation is repeated, and use the *Latency* and *Pitch* triplets accordingly.

# 2.4.3 Using triplets

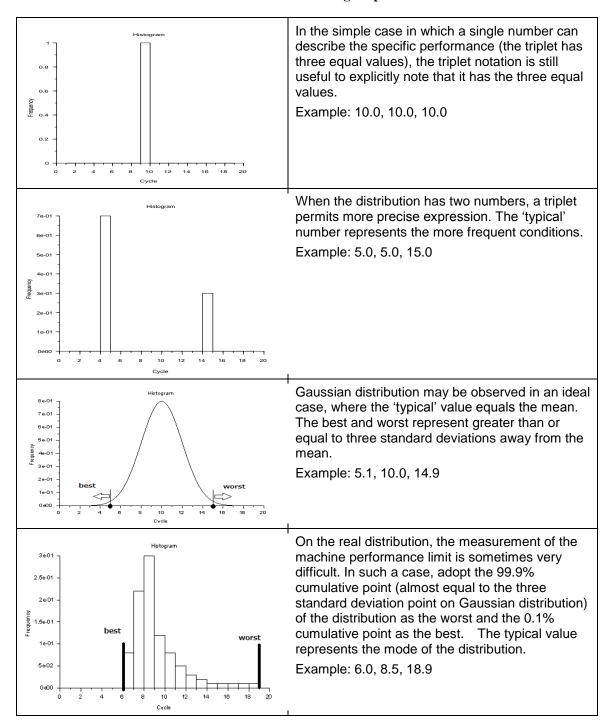

Any factors which influence performance characteristics should be expressed in the triplet of 'best', 'typical' and 'worst' to describe the performance variations. This is described with examples in Table 4. Using Triples).

Please note that, statistically speaking, the 'typical' value is not the average but the mode.

**Table 4. Using Triples**

# 2.5 Software View – what is in and what is not

As said in <u>Introduction</u>, tools should primarily use SHIM to aid developing software that runs on multi-many-core hardware. Therefore, the key strategy in defining the SHIM specification is to describe the hardware but only for the information that is relevant to such tools. We call this a 'software view' of hardware, as opposed to 'hardware view', where the focus would be the physical/electrical means of inter-connects between processing cores, the

$NoC^2$  protocol used to route the memory read request by a particular core, the number of processor pipeline stages, the cache coherency protocol, etc., unless these features matter greatly to some class of tools that aid software development.

It is tempting and relatively easy to include additional hardware properties in SHIM, however this will result in a more complex SHIM XML, requiring more effort to grasp the schema and complicating the effort for tools to use this information. Furthermore, the most critical issue is the challenge to create a SHIM XML in the first place – leading to limited adoption of the SHIM standard.

*The basic principle is to capture the properties that affect the software at the architectural design level.* This is to say, if a design-aid tool uses SHIM to produce an appropriate software design for a particular hardware described by an SHIM XML, then the design should not require modification at the software architectural level at the later stages of system development.

Although the "software architectural design level" is the baseline, it is sometimes difficult to agree on whether a particular hardware property is important. The rule of thumb is that if we cannot derive an actual (even imaginable) use case, the SHIM specification excludes it.

For various reasons, a number of potential hardware properties have not been included into the current specification. One of the primary reasons is that the excluded types of hardware properties are peripheral to existing properties in the specification. Such hardware properties may be included in a future version of the specification, but we decided to take an evolutionary approach and stabilize the more basic properties first.

The most basic properties selected for inclusion are the following: topology, address space, inter-core communication, and performance and configuration.

# 2.6 XML

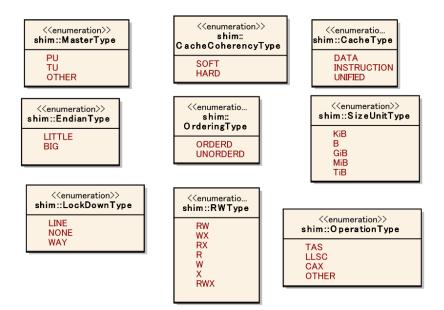

The SHIM interface uses extensible markup language (XML); specifically, the SHIM XML uses the XML Schema (XSD) to define its XML structure. XSD is essentially the same as an UML class diagram. Each SHIM XML file represents a unique hardware, but all must conform to the SHIM XML schema. The UML class diagram representation of SHIM XML schema is shown in Figure 3.

The XML schema allows the definition of the SHIM XML structure, but with the help of a validating parser that reads XML files, the schema also allows validation of SHIM XML. Validating parsers are readily available, both openly and commercially, often bundled with various XML related libraries in many different programming languages.

Therefore, technically speaking, the SHIM XML schema, or the shim.xsd, is the core interface definition of SHIM.

### 2.6.1 Data Binding

A common technique to read XML files is via SAX or DOM libraries. Using XSD, it is possible to generate class libraries in many choices of programming languages by running a schema compiler against the shim.xsd. The generated library includes all the SHIM XML classes of the chosen programming language, with automatically added methods or functions to get and set the data. This allows tools to access hardware properties expressed in a SHIM XML similar to accessing normal objects in their programming languages.

# 2.6.2 Who Creates SHIM XML

The hardware provider is expected to create and provide the SHIM XML, which will then be used by the software tools. On the other hand, a hardware provider may not provide the SHIM XML. If SHIM XML can only be authored by the hardware provider, it can be a significant roadblock in the hardware's adoption. Therefore, <u>Reference authoring tools</u> are made freely available along with the specification. If a user has access to the basic

<sup>&</sup>lt;sup>2</sup> Network on Chip

technical reference manuals, and either simulator or actual hardware (e.g., evaluation board), the <u>Reference</u> <u>authoring tools</u> allows for the creation of the SHIM XML for most multi-many-core hardware in fewer than 1-2 days.

# 2.7 **Configuration**

### 2.7.1 General

There are two different aspects of configuration in SHIM that are needed by software tools. One aspect is the configuration of software tools based on the basic hardware properties (e.g., cluster organization, number of cores, memory size, processor ISA). These are static hardware properties and tools are able to read the SHIM XML file and configure themselves accordingly. The other aspect is configuring the hardware dynamic properties (e.g., clock frequency, various modes and setting for transfer accelerator) that can be modified according to the system design. For dynamic properties, the tools' user is often required to input the configuration, thus the tools must provide a user interface (either command line or graphical). SHIM provides a mechanism called <u>Common</u> <u>Configuration File (CCF)</u>, to serve both for describing the configurable properties and also simultaneously defining the user interface.

Changing the configuration often affects the performance properties. The CCF is designed so that it can also describe how the selection or input value of particular configurable items affects the performance properties.

# 2.7.2 Common Configuration File (CCF)

The CCF extends SHIM to describe configurable hardware elements and also defines a standard way to generate configuration UI by the tools that support it. The CCF describes the configurable items in a file called CCF XML; this is a separate XML file from the SHIM XML. Software tools using SHIM can utilize this mechanism to provide a <u>Configuration tool user interface</u> within its tool, or as a separate standalone tool. When the configuration tool is executed, along with the SHIM XML and CCF, it provides a mechanism to modify the specific parts of SHIM XML, according to the inputs made by the tool user, which can also be automated by the tool.

The SHIM XML and CCF are inter-linked via XPath, the XML Path Language (a query language for selecting nodes from an XML document). In addition, XPath may be used to compute values (e.g., strings, numbers, or Boolean values) from the content of an XML document.

Here is an example of an actual CCF:

| ccf-samp | le-for-shim.xml                                                                                                                                                                                                                                                 | )        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| - 1      | xml version="1.0" encoding="UTF-8"? ↓                                                                                                                                                                                                                           | E E      |

|          | <configurationset name="CCF Sample for SHIM" xmlns:xsi="http://www.w3.org/2001/XMLSchema-instance" xsi:nonamespa<br="">eSchemaLocation="ccf-schema.xsd"&gt;↓</configurationset>                                                                                 | IC       |

| - 3      | <defineset>↓</defineset>                                                                                                                                                                                                                                        |          |

| 4<br>5   | <def name="@sclock" path="/SystemConfiguration/ClockFrequency/@clockValue" uri="&lt;u&gt;shim_sample_data.xml&lt;/u&gt;"></def> ↓ <def name="@cashSize" path="//Cache[@name='UnifiedCache_0_0_0']/@size" uri="&lt;u&gt;shim_sample_data.xml&lt;/u&gt;"></def> ↓ |          |

| 6        | ↓                                                                                                                                                                                                                                                               |          |

| - 7      | <configuration formtype="select" name="System clockValue-Select" path="/SystemConfiguration/ClockFrequency/@clockValue" uri="shim_sample_data.xml">&gt;</configuration>                                                                                         | •        |

| 8        | <item key="value" value="20.0"></item> ↓                                                                                                                                                                                                                        |          |

| 9        | <item key="value" value="40.0"></item> ↓                                                                                                                                                                                                                        |          |

| 10       | <item key="value" value="100.0"></item> ↓                                                                                                                                                                                                                       |          |

| 11       | ↓                                                                                                                                                                                                                                                               |          |

| 12       | <configuration formtype="expression" name="Sample Expression" path="//MasterComponent/ClockFrequency/@clockValue&lt;/td&gt;&lt;td&gt;e&lt;/td&gt;&lt;/tr&gt;&lt;tr&gt;&lt;td&gt;&lt;/td&gt;&lt;td&gt;" uri="shim_sample_data.xml">↓</configuration>             |          |

| 13       | <expression>↓</expression>                                                                                                                                                                                                                                      |          |

| 14       | <description>description</description> ↓                                                                                                                                                                                                                        |          |

| 15       | <exp>@sclock * 2</exp> ↓                                                                                                                                                                                                                                        |          |

| 16       | ↓                                                                                                                                                                                                                                                               |          |

| 17       | ↓                                                                                                                                                                                                                                                               |          |

| 18       | <configuration formtype="text" name="Arch" path="//MasterComponent/@arch" uri="shim_sample_data.xml"></configuration> ↓                                                                                                                                         |          |

| 19       | <configuration formtype="integer" name="nRegister" path="//SharedRegisterCommunication/@nRegister" uri="shim_sam]&lt;br&gt;le_data.xml"></configuration> ↓                                                                                                      | p        |

| 20       | <configuration formtype="float" name="ClockFrequency:clockValue" path="/SystemConfiguration/ClockFrequency/@clockValue" uri="shim_sample_data.xml"></configuration> ↓                                                                                           | <b>v</b> |

| 21       |                                                                                                                                                                                                                                                                 |          |

| 22       | ↓                                                                                                                                                                                                                                                               |          |

|          | [ÉOF]                                                                                                                                                                                                                                                           |          |

|          | Unicode(UTF-8) 911pt                                                                                                                                                                                                                                            |          |

# Figure 7. CCF example

This CCF, when opened by a CCF capable tool, will dynamically create a GUI like below (this is a CCF sample application available with source codes from MCA).

#### **SHIM Specification V1.00**

| CCF Sample Application                                                                                                                                |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| OpenCCF Configure All                                                                                                                                 |          |

| System clockValue-Select FormType select Configurre Reusit 20.0                                                                                       | I enable |

| System clockValue-Select     20.0     VRI     shim_sample_data.xml       XPath     /SystemConfiguration/ClockFrequency/@clockValue                    | Je       |

| Sample Expression FormType expression Configurre Reuslt 80.0                                                                                          | ✓ enable |

| Sample Expression         @sclock * 2           URI         shim_sample_data.xml           XPath         //MasterComponent/ClockFrequency/@clockValue |          |

| Arch FormType text Configurre Reuslt Generic I enable                                                                                                 |          |

| Arch Generic URI shim_sample_data.xml<br>XPath //MasterComponent/@arch                                                                                |          |

| nRegister FormType integer Configurre Reusit 32                                                                                                       |          |

| nRegister 32 URI shim_sample_data.xml<br>XPath //SharedRegisterCommunication/@nRegister                                                               |          |

| ClockFrequency:clockValue FormType float Configurre Reuslt 40                                                                                         | ✓ enable |

| ClockFrequency:clockValue 40 URI shim_sample_data.xml XPath /SystemConfiguration/ClockFrequency/@clockValue                                           | ie       |

| BooleValue Sample FormType bool Configurre Reusit false                                                                                               | nable    |

| BooleValue Sample false URI *file*<br>XPath *xpath*                                                                                                   |          |

|                                                                                                                                                       |          |

|                                                                                                                                                       |          |

### Figure 8. GUI generated by CCF

Please refer to <u>Common Configuration File (CCF)</u>.

# 2.8 **Reference Authoring Tools**

In addition to the specification itself, SHIM also provides a free set of reference authoring tools. As a reference, anyone can provide their own version of the SHIM authoring tools. The Multicore Association provides the reference authoring tool, SHIM Editor, for the following reasons:

- 1. Easy authoring of SHIM XML to enable better adoption

- 2. Serves as a sample SHIM application with source code

# 2.9 **Roadmap**

The first version of SHIM contains the fundamental and critical hardware properties that many tools will find useful. However, as mentioned in <u>Software view - what is in and what is not</u>, some items have not been covered in this first version. SHIM is an open technology and wider adoption will fuel its innovative use; this may require enhancements to the specification and we would like to remain open to such changes.

Properties that are under consideration for future versions of the spec include: debug/trace, power consumption, and basic peripheral components. A few other items are worth mentioning such as componentization of SHIM XML, hardware-related software properties, and schema refinement for smaller XML.

### 2.9.1 Componentization of SHIM XML

The current version of SHIM must stand alone, meaning that a SHIM XML file should describe an executable hardware platform (e.g., a virtual simulator or an actual hardware board). However, a dedicated multi-many-core chip is rarely designed for each board, therefore, the same chip is often deployed in multiple boards. This means that separate SHIM XML files must exist for each board, though the SHIM XML description of the multi-many-core chip description is redundant for these two files.

Once SHIM's use starts to spread, it is natural to reuse a particular component description in a SHIM XML file among multiple SHIM XML files. This is essentially componentization of SHIM XML, a feature already under consideration for inclusion in the next major version of SHIM. Meanwhile, one can use an existing SHIM XML file resembling your target hardware as a basis of authoring a new SHIM XML file. SHIM Editor indeed supports editing of an existing SHIM XML file.

A challenge of componentizing SHIM XML is that a SHIM XML class, such as *MasterComponent*, contains properties that are static for the hardware board design it is being included with, and also properties that may differ depending on how it is integrated into a particular hardware board. The two must be decoupled in order to reuse the SHIM XML description of the *MasterComponent*. One idea is to use <u>Common Configuration File (CCF)</u>, which allows for adjusting the performance value based on some other information, as long as it can be found in the final SHIM XML file or somewhere within the CCF.

Also along with the componentization of SHIM XML itself, we are investigating the possibility to align SHIM with IP-XACT where appropriate, to ease SHIM XML authoring tools ability to support importing IP-XACT XML files to semi-automate authoring a SHIM XML using the relevant information contained in IP-XACT. The objects contained in the *ComponentSet*, at least the topology part and the object names, should be importable, while others are unique to SHIM XML and must be added.

### 2.9.2 Hardware-Related Software Properties

In addition to the hardware properties that SHIM describes, some tools have a dependency on the system software properties such as the operating system and even some middleware. For example, for a parallelization design aid tool such as a parallelizing compiler, the performance of OS mutual exclusion primitives is critical in deciding on an appropriate lock mechanism for particular processing. Similarly, the tool may need to know the performance of some message passing mechanism. Currently, this kind of information is not included in SHIM, partly because it will require separate SHIM XML files for different system software implementations, along with the library interface definition; a future version of SHIM may extend its coverage into this kind of information.

### 2.9.3 Schema Refinement for Smaller XML

The SHIM schema is intended to be simple, while allowing it to support both homogeneous and heterogeneous hardware. This has led to using repetitive sets of lines in the XML for homogenous hardware that have multiple instances of the same component, like a hardware composed of multiple instances of the same cluster configuration. If the clusters are heterogeneous, with each cluster having a different configuration of processing cores, then the number of XML lines does not change but they will have different lines. If SHIM can provide a mechanism to express the redundancy in the schema, the size of SHIM XML file for homogenous hardware can be reduced. We intend to consider this along with <u>Componentization of SHIM XML</u>.

# 3. SHIM Interface

The major part of the SHIM interface is the SHIM XML schema itself. Therefore, understanding the schema comprises the major part of understanding the interface. The basics are described in the chapter <u>SHIM Concepts</u> and it assumes the schema is divided into the following groups:

- Enumeration

- SystemConfiguration

- ComponentSet

- AddressSpaceSet

- CommunicationSet

For each group above, the schema and the description are explained in the following sections. For each object or XML element contained in each group, the description and example XML are provided.

The schema is converted into different programming language bindings, using various schema compilers. The SHIM specification does not specify the programming language as this can vary according to the nature of the tools and intended use cases. However, Java is assumed to be one of the primary languages used and the Java class library interface of SHIM, called the SHIM API library, is also provided. Some utility interfaces are defined along with the reference implementation in Java to further ease the programming using of the SHIM class libraries.

The following sections describe each part, detailing the XML elements and their attributes, along with a pointer to the Java class library interface.

# 3.1 shim.xsd

The SHIM XML schema file. Please refer to the following sections for description of elements.

```

<?xml version="1.0"?>

<xs:schema xmlns:xs="http://www.w3.org/2001/XMLSchema">

<xs:element name="ComponentSet" type="ComponentSet"/>

<xs:complexType name="ComponentSet">

<xs:sequence>

<xs:element name="ComponentSet" type="ComponentSet" minOccurs="0"</pre>

maxOccurs="unbounded"/>

<xs:element name="SlaveComponent" type="SlaveComponent" minOccurs="0"</pre>

maxOccurs="unbounded"/>

<xs:element name="MasterComponent" type="MasterComponent" minOccurs="0"</pre>

maxOccurs="unbounded"/>

<xs:element name="Cache" type="Cache" minOccurs="0" maxOccurs="unbounded"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

</xs:complexType>

<xs:element name="SlaveComponent" type="SlaveComponent"/>

<xs:complexType name="SlaveComponent">

<xs:annotation>

<xs:documentation>Memory</xs:documentation>

</xs:annotation>

<xs:sequence/>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="id" use="required" type="xs:ID"/>

<xs:attribute name="size" use="required" type="xs:int"/>

<xs:attribute name="sizeUnit" use="required" type="SizeUnitType"/>

<xs:attribute name="rwType" use="required" type="RWType"/>

</xs:complexType>

<xs:element name="MasterComponent" type="MasterComponent"/>

<xs:complexType name="MasterComponent">

<xs:sequence>

<xs:element name="CommonInstructionSet" type="CommonInstructionSet" minOccurs="0"</pre>

maxOccurs="1"/>

<xs:element name="Cache" type="Cache" minOccurs="0" maxOccurs="unbounded"/>

<xs:element name="ClockFrequency" type="ClockFrequency" minOccurs="0"</pre>

maxOccurs="1"/>

<xs:element name="AccessTypeSet" type="AccessTypeSet" minOccurs="1"</pre>

maxOccurs="1"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="id" use="required" type="xs:ID"/>

<xs:attribute name="masterType" use="required" type="MasterType"/>

<xs:attribute name="arch" use="required" type="xs:string"/>

<xs:attribute name="archOption" use="optional" type="xs:string"/>

<xs:attribute name="pid" use="optional" type="xs:string"/>

<xs:attribute name="nThread" use="optional" type="xs:int"/>

<xs:attribute name="endian" use="optional" type="EndianType"/>

</xs:complexType>

<xs:simpleType name="RWType">

<xs:restriction base="xs:string">

<xs:enumeration value="RW"/>

<xs:enumeration value="WX"/>

<xs:enumeration value="RX"/>

<xs:enumeration value="R"/>

<xs:enumeration value="W"/>

<xs:enumeration value="X"/>

<xs:enumeration value="RWX"/>

</xs:restriction>

</xs:simpleType>

<xs:element name="AddressSpaceSet" type="AddressSpaceSet"/>

<xs:complexType name="AddressSpaceSet">

<xs:sequence>

<xs:element name="AddressSpace" type="AddressSpace" minOccurs="1"</pre>

maxOccurs="unbounded"/>

</xs:sequence>

</xs:complexType>

<xs:element name="AddressSpace" type="AddressSpace"/>

<xs:complexType name="AddressSpace">

<xs:sequence>

<xs:element name="SubSpace" type="SubSpace" minOccurs="0" maxOccurs="unbounded"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="id" use="required" type="xs:ID"/>

</xs:complexType>

<xs:element name="SubSpace" type="SubSpace"/>

<xs:complexType name="SubSpace">

```

```

<xs:sequence>

<xs:element name="MemoryConsistencyModel" type="MemoryConsistencyModel"</pre>

minOccurs="0" maxOccurs="unbounded"/>

<xs:element name="MasterSlaveBindingSet" type="MasterSlaveBindingSet"</pre>

minOccurs="0" maxOccurs="1"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="id" use="required" type="xs:ID"/>

<xs:attribute name="start" use="required" type="xs:long"/>

<xs:attribute name="end" use="required" type="xs:long"/>

<xs:attribute name="endian" use="optional" type="EndianType"/>

</xs:complexType>

<xs:simpleType name="MasterType">

<xs:restriction base="xs:string">

<xs:enumeration value="PU">

<xs:annotation>

<xs:documentation>Processing Unit</xs:documentation>

</xs:annotation>

</xs:enumeration>

<xs:enumeration value="TU">

<xs:annotation>

<xs:documentation>Transffer Unit</xs:documentation>

</xs:annotation>

</xs:enumeration>

<xs:enumeration value="OTHER"/>

</xs:restriction>

</xs:simpleType>

<xs:element name="Instruction" type="Instruction"/>

<xs:complexType name="Instruction">

<xs:sequence>

<xs:element name="Performance" type="Performance" minOccurs="1" maxOccurs="1"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

</xs:complexType>

<xs:element name="InterruptCommunication" type="InterruptCommunication"/>

<xs:complexType name="InterruptCommunication">

<xs:complexContent>

<xs:extension base="AbstractCommunication">

<xs:sequence/>

</xs:extension>

</xs:complexContent>

</xs:complexType>

<xs:element name="Latency" type="Latency"/>

<xs:complexType name="Latency">

<xs:complexContent>

<xs:extension base="AbstractPerformance">

<xs:sequence/>

</xs:extension>

</xs:complexContent>

</xs:complexType>

<xs:element name="AbstractPerformance" type="AbstractPerformance"/>

<xs:complexType name="AbstractPerformance" abstract="true">

<xs:sequence/>

<xs:attribute name="best" use="optional" type="xs:float"/>

<xs:attribute name="typical" use="required" type="xs:float"/>

<xs:attribute name="worst" use="optional" type="xs:float"/>

</xs:complexType>

<xs:element name="Pitch" type="Pitch"/>

<xs:complexType name="Pitch">

<xs:complexContent>

<xs:extension base="AbstractPerformance">

<xs:sequence/>

</xs:extension>

</xs:complexContent>

</xs:complexType>

<xs:element name="MasterSlaveBinding" type="MasterSlaveBinding"/>

<xs:complexType name="MasterSlaveBinding">

<xs:sequence>

<xs:element name="Accessor" type="Accessor" minOccurs="1" maxOccurs="unbounded"/>

</xs:sequence>

<xs:attribute name="slaveComponentRef" use="required" type="xs:IDREF"/>

</xs:complexType>

<xs:element name="CommunicationSet" type="CommunicationSet"/>

<xs:complexType name="CommunicationSet">

<xs:sequence>

```

```

<xs:element name="SharedRegisterCommunication" type="SharedRegisterCommunication"</pre>

minOccurs="0" maxOccurs="unbounded"/>

<xs:element name="SharedMemoryCommunication" type="SharedMemoryCommunication"

minOccurs="0" maxOccurs="unbounded"/>

<xs:element name="EventCommunication" type="EventCommunication" minOccurs="0"</pre>

maxOccurs="unbounded"/>

<xs:element name="FIFOCommunication" type="FIFOCommunication" minOccurs="0"</pre>

maxOccurs="unbounded"/>

<xs:element name="InterruptCommunication" type="InterruptCommunication"</pre>

minOccurs="0" maxOccurs="unbounded"/>

</xs:sequence>

</xs:complexType>

<xs:element name="AbstractCommunication" type="AbstractCommunication"/>

<xs:complexType name="AbstractCommunication" abstract="true">

<xs:sequence>

<xs:element name="ConnectionSet" type="ConnectionSet" minOccurs="0"</pre>

maxOccurs="1"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

</xs:complexType>

<xs:element name="Connection" type="Connection"/>

<xs:complexType name="Connection">

<xs:sequence>

<xs:element name="Performance" type="Performance" minOccurs="0"</pre>

maxOccurs="unbounded"/>

</xs:sequence>

<xs:attribute name="from" use="required" type="xs:IDREF">

<xs:annotation>

<xs:documentation>Reference to the instance of

MasterComponent</xs:documentation>

</xs:annotation>

</xs:attribute>

<xs:attribute name="to" use="required" type="xs:IDREF">

<xs:annotation>

<xs:documentation>Reference to the instance of

MasterComponent</xs:documentation>

</xs:annotation>

</xs:attribute>

</xs:complexType>

<xs:element name="PerformanceSet" type="PerformanceSet"/>

<xs:complexType name="PerformanceSet">

<xs:sequence>

<xs:element name="Performance" type="Performance" minOccurs="0"</pre>

maxOccurs="unbounded"/>

</xs:sequence>

</xs:complexType>

<xs:element name="FIFOCommunication" type="FIFOCommunication"/>

<xs:complexType name="FIFOCommunication">

<xs:complexContent>

<xs:extension base="AbstractCommunication">

<xs:sequence/>

<xs:attribute name="dataSize" use="required" type="xs:int"/>

<xs:attribute name="dataSizeUnit" use="optional" type="SizeUnitType"/>

<xs:attribute name="queueSize" use="required" type="xs:int"/>

</xs:extension>

</xs:complexContent>

</xs:complexType>

<xs:element name="CommonInstructionSet" type="CommonInstructionSet"/>

<xs:complexType name="CommonInstructionSet">

<xs:sequence>

<xs:element name="Instruction" type="Instruction" minOccurs="1"</pre>

maxOccurs="unbounded"/>

</xs:sequence>

<rs:attribute name="name" use="required" type="xs:string"/>

</xs:complexType>

<xs:element name="Cache" type="Cache"/>

<xs:complexType name="Cache">

<xs:sequence>

<xs:element name="cacheRef" type="xs:IDREF" minOccurs="0" maxOccurs="unbounded"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="id" use="required" type="xs:ID"/>

<xs:attribute name="cacheType" use="required" type="CacheType">

<xs:annotation>

<xs:documentation>soft / hard</xs:documentation>

```

```

</xs:annotation>

</xs:attribute>

<xs:attribute name="cacheCoherency" use="required" type="CacheCoherencyType"/>

<xs:attribute name="size" use="required" type="xs:int"/>

<xs:attribute name="sizeUnit" use="required" type="SizeUnitType"/>

<xs:attribute name="nWay" use="optional" type="xs:int"/>

<xs:attribute name="lineSize" use="optional" type="xs:int"/>

<xs:attribute name="lockDownType" use="optional" type="LockDownType"/>

</xs:complexType>

<xs:element name="SystemConfiguration" type="SystemConfiguration"/>

<xs:complexType name="SystemConfiguration">

<xs:sequence>

<xs:element name="ComponentSet" type="ComponentSet" minOccurs="1" maxOccurs="1"/>

<xs:element name="CommunicationSet" type="CommunicationSet" minOccurs="0"</pre>

maxOccurs="1"/>

<xs:element name="AddressSpaceSet" type="AddressSpaceSet" minOccurs="0"</pre>

maxOccurs="1"/>

<xs:element name="ClockFrequency" type="ClockFrequency" minOccurs="1"</pre>

maxOccurs="1"/>

</xs:sequence>

<xs:attribute name="name" use="required" type="xs:string"/>

<xs:attribute name="shimVersion" use="required" type="xs:string"/>

</xs:complexType>

<xs:element name="ConnectionSet" type="ConnectionSet"/>

<xs:complexType name="ConnectionSet">

<xs:sequence>

<xs:element name="Connection" type="Connection" minOccurs="1"</pre>

maxOccurs="unbounded"/>

</xs:sequence>

</xs:complexType>

<xs:simpleType name="CacheCoherencyType">

<xs:restriction base="xs:string">

<xs:enumeration value="SOFT"/>

<xs:enumeration value="HARD"/>

</xs:restriction>

</xs:simpleType>

<xs:element name="MemoryConsistencyModel" type="MemoryConsistencyModel"/>

<xs:complexType name="MemoryConsistencyModel">

<xs:sequence/>

<xs:attribute name="rawOrdering" use="optional" type="OrderingType">

<xs:annotation>

<xs:documentation>Read After Write</xs:documentation>

</xs:annotation>

</xs:attribute>

<xs:attribute name="warOrdering" use="optional" type="OrderingType">

<xs:annotation>

<xs:documentation>Write After Read</xs:documentation>

</xs:annotation>

</xs:attribute>

<xs:attribute name="wawOrdering" use="optional" type="OrderingType">

<xs:annotation>

<xs:documentation>Write After Write</xs:documentation>

</xs:annotation>

</xs:attribute>

<xs:attribute name="rarOrdering" use="optional" type="OrderingType"/>

</xs:complexType>

<xs:simpleType name="OrderingType">

<xs:restriction base="xs:string">

<xs:enumeration value="ORDERD"/>

<xs:enumeration value="UNORDERD"/>

</xs:restriction>

</xs:simpleType>

<xs:simpleType name="EndianType">

<xs:restriction base="xs:string">

<xs:enumeration value="LITTLE"/>

<xs:enumeration value="BIG"/>

</xs:restriction>

</xs:simpleTvpe>

<xs:element name="SharedRegisterCommunication" type="SharedRegisterCommunication"/>

<xs:complexType name="SharedRegisterCommunication">

<xs:complexContent>

<xs:extension base="AbstractCommunication">

<xs:sequence/>

<xs:attribute name="dataSize" use="required" type="xs:int"/>

<xs:attribute name="dataSizeUnit" use="required" type="SizeUnitType"/>

```

```

<xs:attribute name="nRegister" use="required" type="xs:int"/>

</xs:extension>

</xs:complexContent>

</xs:complexType>

<xs:element name="SharedMemoryCommunication" type="SharedMemoryCommunication"/>

<xs:complexType name="SharedMemoryCommunication">

<xs:complexContent>

<xs:extension base="AbstractCommunication">

<xs:sequence/>

<xs:attribute name="operationType" use="optional" type="OperationType"/>

<xs:attribute name="dataSize" use="optional" type="xs:int"/>

<xs:attribute name="dataSizeUnit" use="optional" type="SizeUnitType"/>

<xs:attribute name="addressSpaceRef" use="optional" type="xs:IDREF"/>

<xs:attribute name="subSpaceRef" use="optional" type="xs:IDREF"/>

</xs:extension>

</xs:complexContent>

</xs:complexTvpe>

<xs:element name="EventCommunication" type="EventCommunication"/>

<xs:complexType name="EventCommunication">

<xs:complexContent>

<xs:extension base="AbstractCommunication">